# DIGITAL DESIGNUSING ABEL

```

node istype

Accum

= [q3..q0];

q3..q0

Mcontrol

state_diagram Mcontrol

II Clear the status

Il Clear the accumulator

state IDLE: if (start) then

Mstate1 with (

:= 0;

Accum := 0;

II Hold the status

II Hold the result value

else IDLE with (

:= done.fb;

Accum := Accum.fb;

II Test bit 0 of operand B

Il Shift/add result into accumult

II A into Shift/add

when (B[0] == 1) then

state Mstate1:

F[7..0] = A

Accum := S;

Il Test bit 1 of operand B

goto Mstate2;

Il Shift A 1 bit left into F

Il Shift/add result into accu

when (B[1] == 1) then

state Mstate2:

F[8.1] = A

Accum := S;

Il Test bit 2 of operand

goto Mstate3;

Il Shift A 2 bits left into

Il Shift/add result into a

when (B[2] == 1) then

state Mstate3:

```

DAVID PELLERIN / MICHAEL HOLLEY

### Digital Design Using ABEL

David Pellerin and Michael Holley

PTR Prentice Hall Englewood Cliffs, New Jersey 07632 Library of Congress Cataloging-in-Publication Data Pellerin, David

Digital design using ABEL / David Pellerin, Michael Holley

p. cm. Includes index.

ISBN 0-13-605874-4

1. Programmable logic devices--Design--Data processing. 2. Logic design--Data processing 3. ABEL (Computer program language) 1. Holley, Michael. II. Title TK7872.L64P39 1994 621.39'5--dc20 93-39558

93-39558 CIP

Editorial/production supervision: Camille Trentacoste

Cover design: Wanda Lubelska Manufacturing manager: Alexis Heydt Acquisitions editor: Karen Gettman

© 1994 by PTR Prentice Hall Prentice-Hall, Inc. A Paramount Communications Company Englewood Cliffs, New Jersey 07632

Altera is a trademark of Altera Corporation.

Data I/O® is a registered trademark and ABEL™ is a trademark of Data I/O Corporation.

PAL™ is a trademark of Advanced Micro Devices.

GAL™ and Lattice are trademarks of Lattice Semiconductor Corporation.

Microsoft® and MS-DOS® are registered trademarks and Windows™ is a trademark of Microsoft.

IBM® and AT® are registered trademarks of International Business Machines Corporation.

PEEL™ is a trademark of International CMOS Technology, Incorporated.

The information in Appendix C is provided courtesy of Data I/O Corporation.

The publisher offers discounts on this book when ordered in bulk quantities. For more information, contact:

Corporate Sales Department PTR Prentice Hall 113 Sylvan Avenue Englewood Cliffs, NJ 07632

Phone: 201-592-2863 FAX: 201-592-2249

All rights reserved. No part of this book may be reproduced, in any form or by any means, without permission in writing from the publisher.

Printed in the United States of America 10 9 8 7 6 5 4 3 2 1

D = 1.3 - 60.5874 - 4

Prentice-Hall International (UK) Limited, London

Prentice-Hall of Australia Pty. Limited, Sydney

Prentice-Hall Canada Inc., Toronto

Prentice-Hall Hispanoamericana, S.A., Mexico

Prentice-Hall of India Private Limited, New Delhi

Prentice-Hall of Japan, Inc., Tokyo

Simon & Schuster Asia Pte. Ltd., Singapore

Editora Prentice-Hall do Brasil, Ltda., Rto de Janetro

# Contents

|           | Preface, vii                              |

|-----------|-------------------------------------------|

| Chapter 1 | Introduction, 1                           |

|           | 1.1 DESIGN ENTRY USING ABEL, 1            |

| Chapter 2 | Combinational Circuits, 9                 |

|           | 2.1 LOGIC CIRCUITS AND LOGIC FUNCTIONS, 9 |

|           | 2.2 BOOLEAN ALGEBRA, 14                   |

|           | 2.3 USING BOOLEAN ALGEBRA IN ABEL, 21     |

|           | 2.4 REFERENCES, 22                        |

| Chapter 3 | Logic Minimization, 23                    |

|           | 3.1 TWO-LEVEL MINIMIZATION, 23            |

|           | 3.2 ON-SETS, OFF-SETS, AND DC-SETS, 40    |

|           | 3.3 MULTIPLE-OUTPUT MINIMIZATION, 43      |

|           | 3.4 MULTILEVEL OPTIMIZATION, 44           |

|           | 3.5 OPTIMIZING WITH EXCLUSIVE-ORS, 47     |

|           | 3.6 REFERENCES, 52                        |

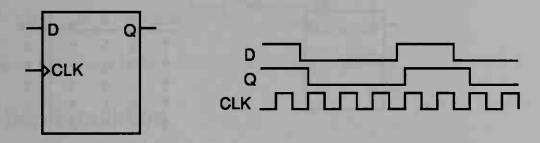

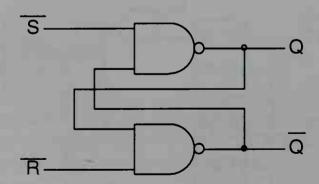

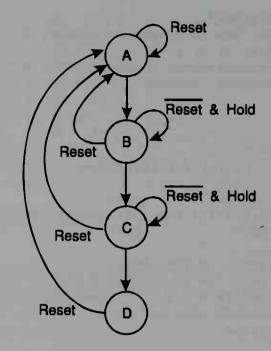

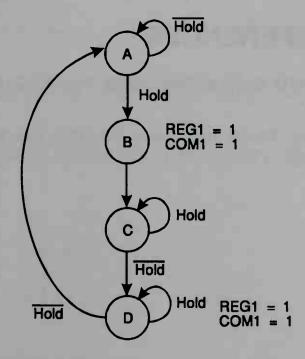

| Chapter 4 | Sequential Circuits, 55                   |

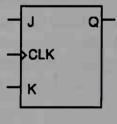

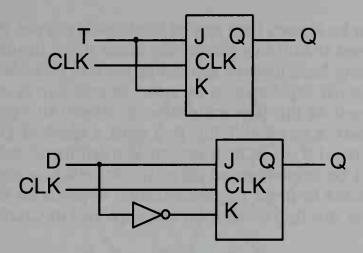

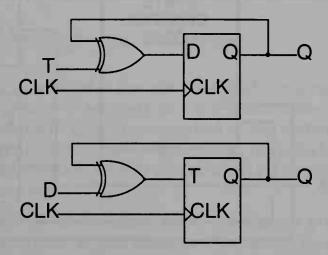

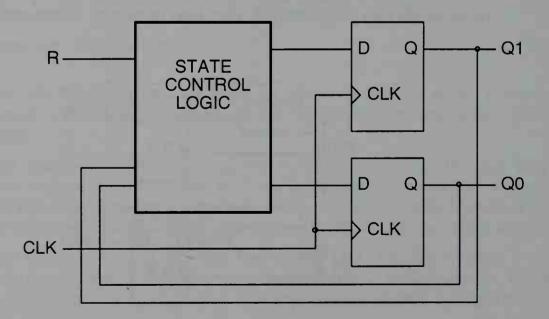

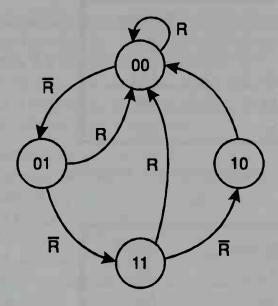

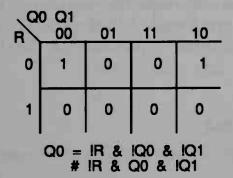

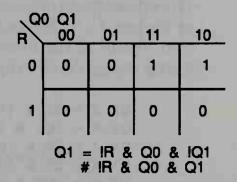

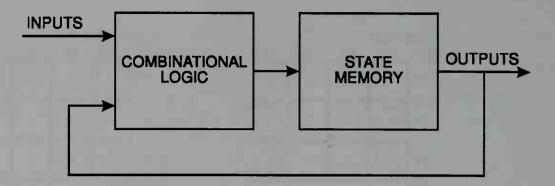

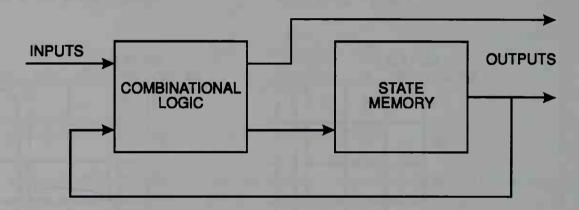

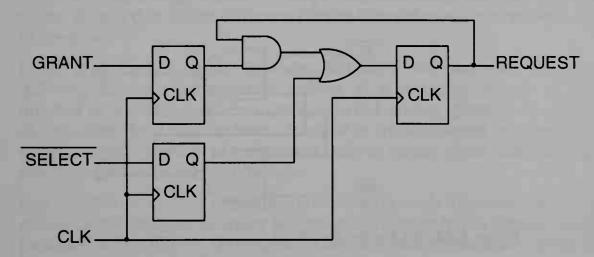

|           | 4.1 SYNCHRONOUS SEQUENTIAL CIRCUITS, 55   |

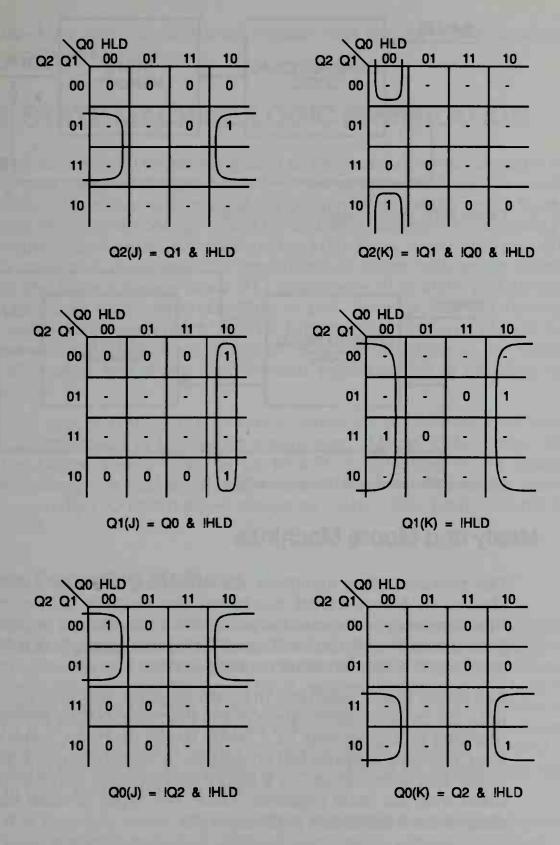

|           | 4.2 STATE MACHINE LOGIC MINIMIZATION, 67  |

|           | 4.3 METASTABILITY, 68                     |

|           | 4.4 ASYNCHRONOUS STATE MACHINES, 70       |

|           | 4.5 REFERENCES, 76                        |

#### Chapter 5 Using ABEL, 77

- 5.1 LANGUAGE OVERVIEW, 77

- 5.2 USING ABEL EQUATIONS, 78

- 5.3 USING TRUTH TABLES, 81

- 5.4 USING STATE DIAGRAMS, 85

- 5.5 REFERENCES, 88

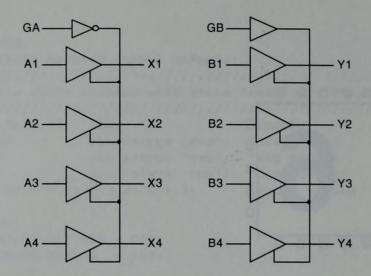

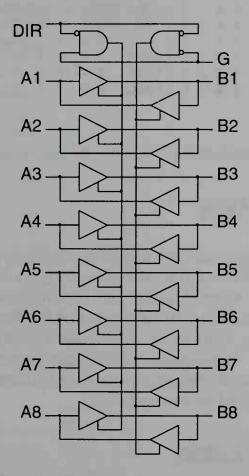

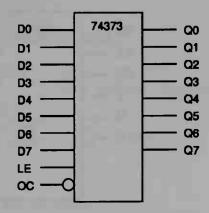

#### Chapter 6 Basic TTL Logic Functions, 91

- 6.1 BUFFERS, 91

- 6.2 LATCHES, 94

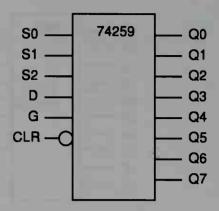

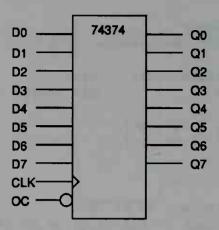

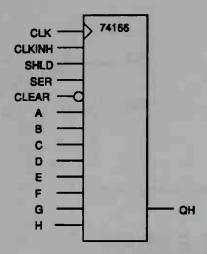

- 6.3 REGISTERS, 98

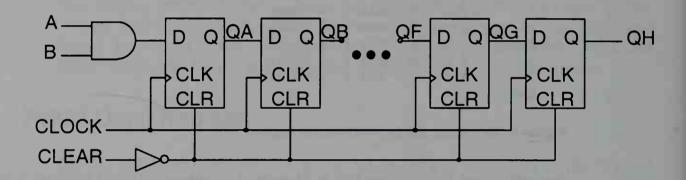

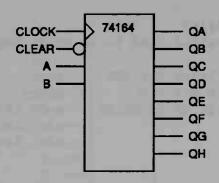

- 6.4 SHIFT REGISTERS, 98

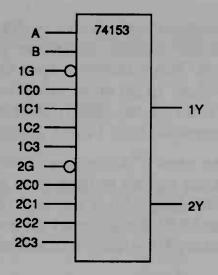

- 6.5 MULTIPLEXERS, 104

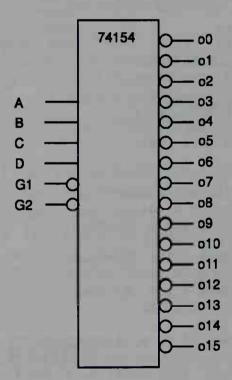

- 6.6 DEMULTIPLEXERS, 104

- 6.7 REFERENCES, 108

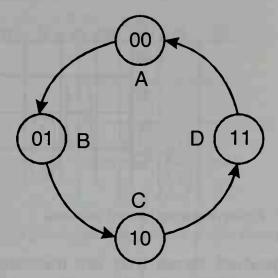

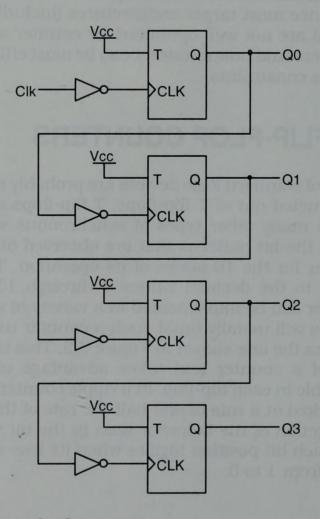

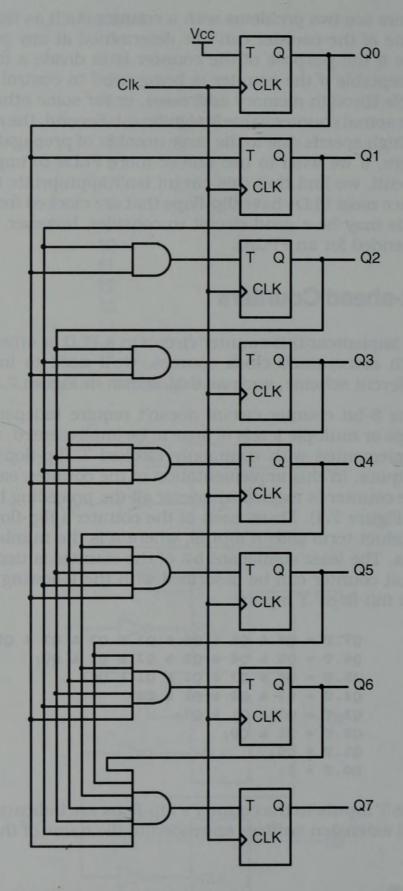

#### Chapter 7 Counters, 109

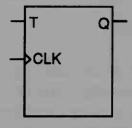

- 7.1 T FLIP-FLOP COUNTERS. 109

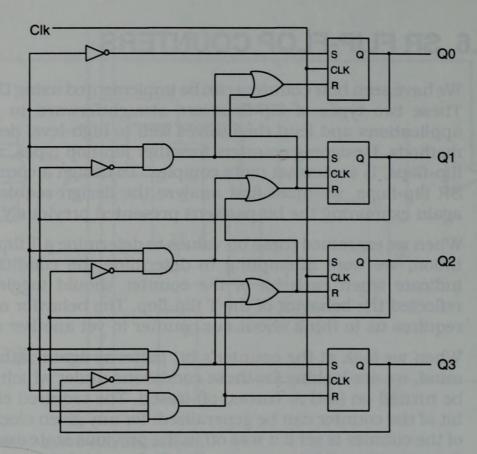

- 7.2 D FLIP-FLOP COUNTERS, 113

- 7.3 LOADABLE COUNTERS, 114

- 7.4 COUNTER RESET SCHEMES, 115

- 7.5 POLARITY CONSIDERATIONS, 117

- 7.6 SR FLIP-FLOP COUNTERS. 119

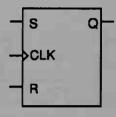

- 7.7 UP AND DOWN COUNTERS, 119

- 7.8 ARBITRARY LENGTH COUNTERS, 122

- 7.9 CHAINED COUNTERS, 127

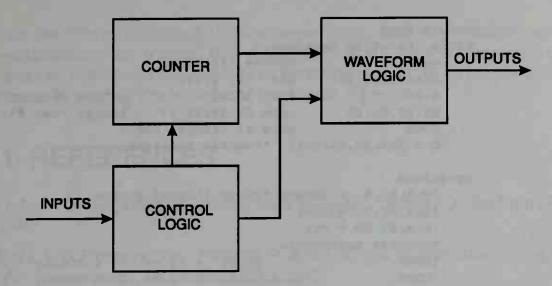

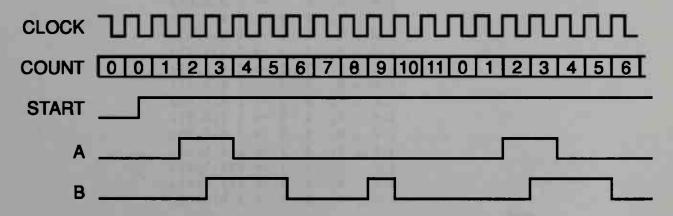

- 7.10 WAVEFORM GENERATOR, 127

- 7.11 REFERENCES. 131

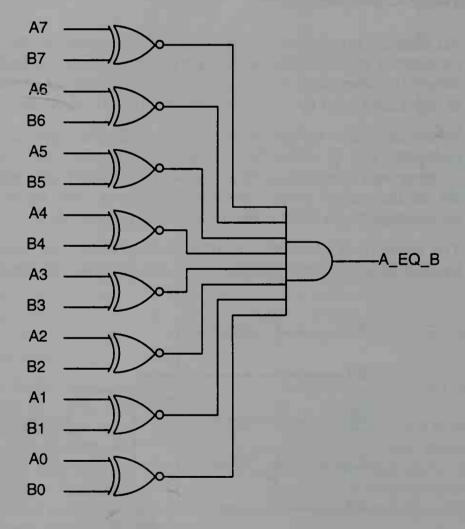

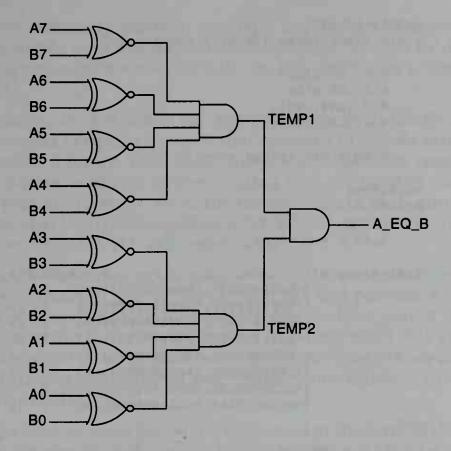

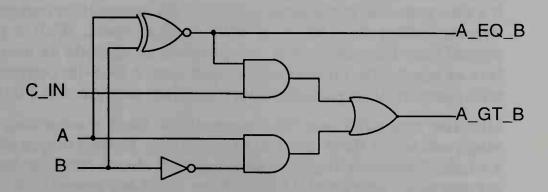

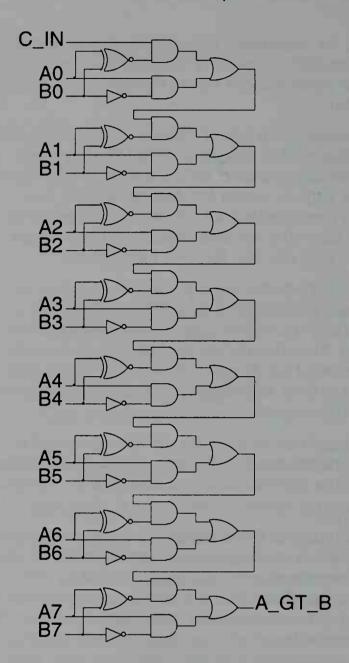

#### Chapter 8 Decoders and Comparators, 133

- 8.1 ADDRESS DECODERS, 133

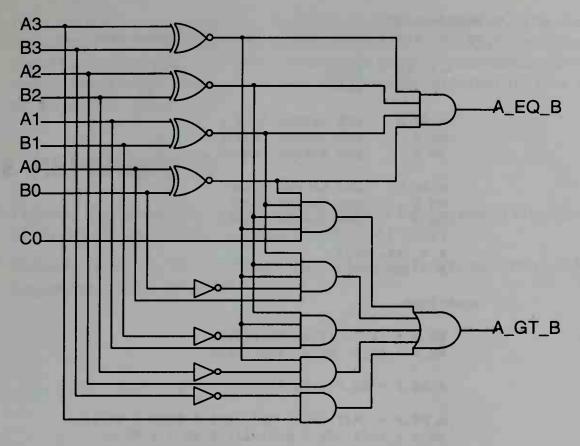

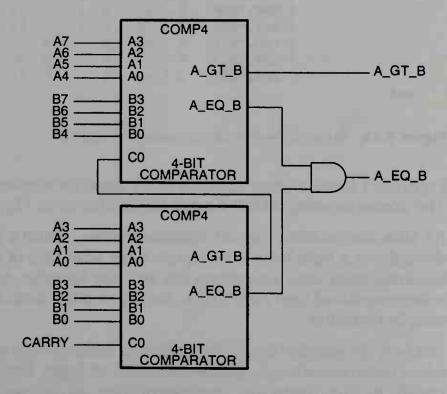

- 8.2 COMPARATORS, 135

#### 8.3 REFERENCES, 145

#### Chapter 9 Arithmetic Functions, 147

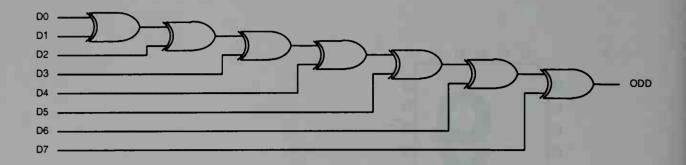

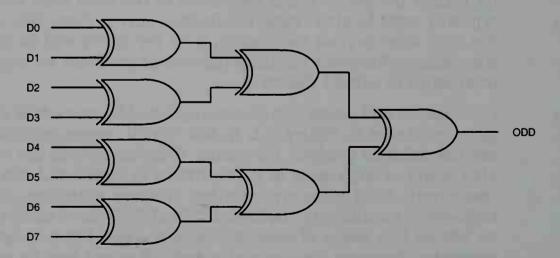

- 9.1 PARITY DETECTION, 147

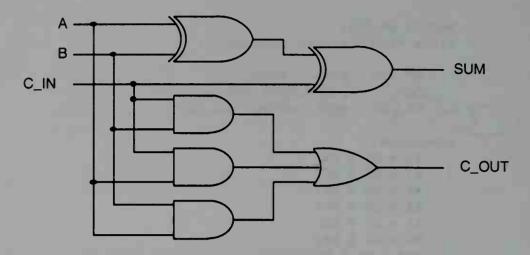

- 9.2 ADDERS, 150

- 9.3 HIGH-LEVEL ADDER EQUATIONS, 152

- 9.4 FAST CARRY (LOOK-AHEAD) ADDERS, 153

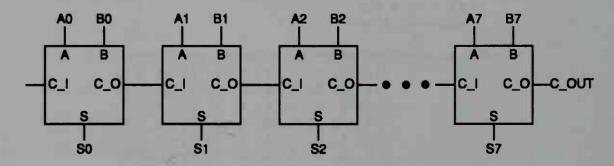

- 9.5 CHAINED ADDERS, 153

- 9.6 SUBTRACTERS. 155

- 9.7 FIBONACCI SEQUENCE GENERATOR, 155

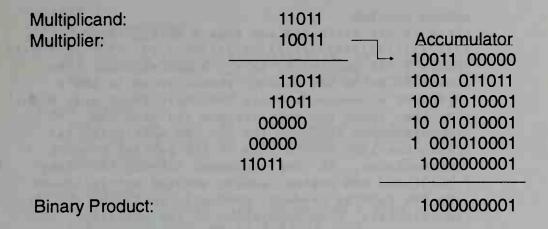

- 9.8 BINARY MULTIPLICATION, 158

- 9.9 REFERENCES, 163

#### Chapter 10 Code Converters, 165

- 10.1 BCD TO SEVEN-SEGMENT DECODER, 165

- 10.2 GRAY-CODE CONVERTERS, 167

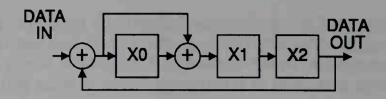

- 10.3 CRC GENERATORS, 167

- 10.4 REFERENCES, 175

#### Chapter 11 Describing State Machines, 177

- 11.1 STATE TRANSITION TABLES, 177

- 11.2 USING STATE DIAGRAMS, 180

- 11.3 POWER-UP AND ILLEGAL STATES. 181

- 11.4 ADDING STATE BITS TO SAVE LOGIC. 185

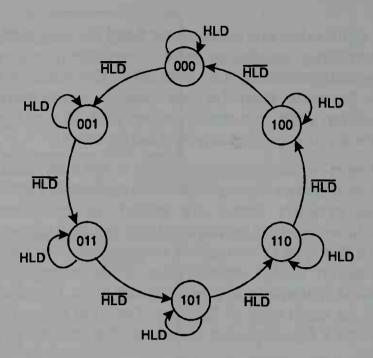

- 11.5 ONE-HOT STATE ENCODING, 188

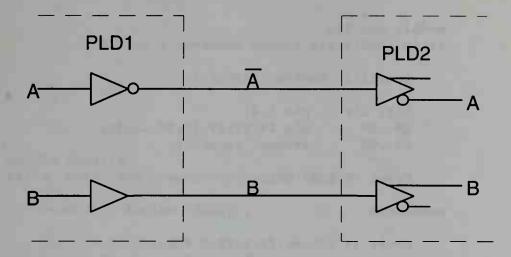

- 11.6 STATE MACHINE PARTITIONING, 188

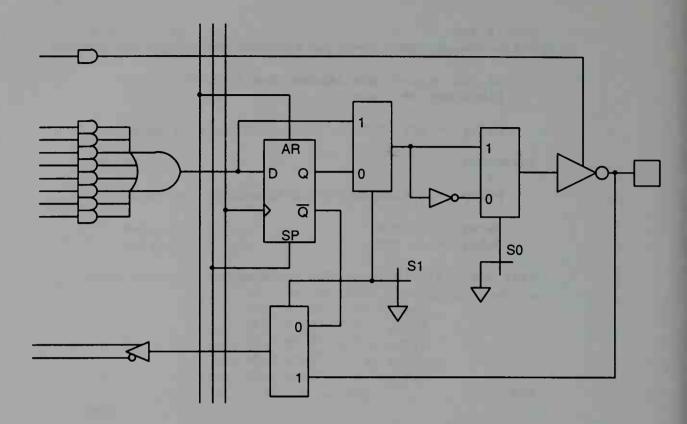

- 11.7 ASYNCHRONOUS STATE MACHINES, 198

- 11.8 REFERENCES, 201

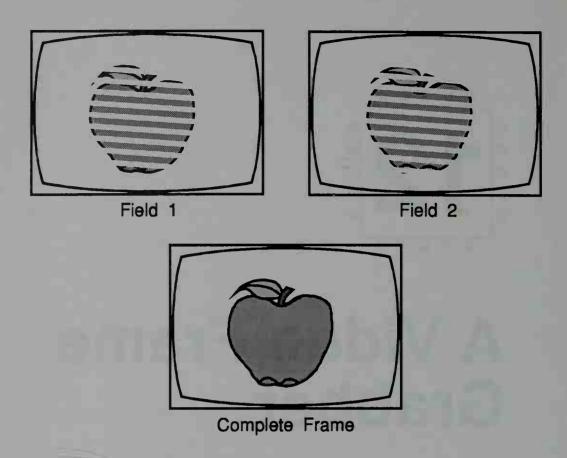

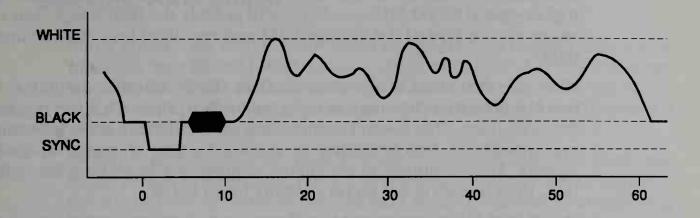

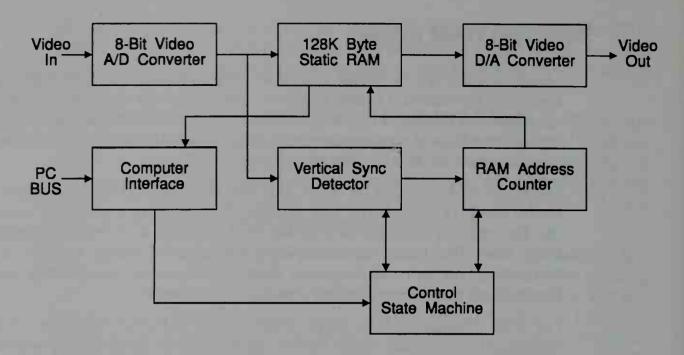

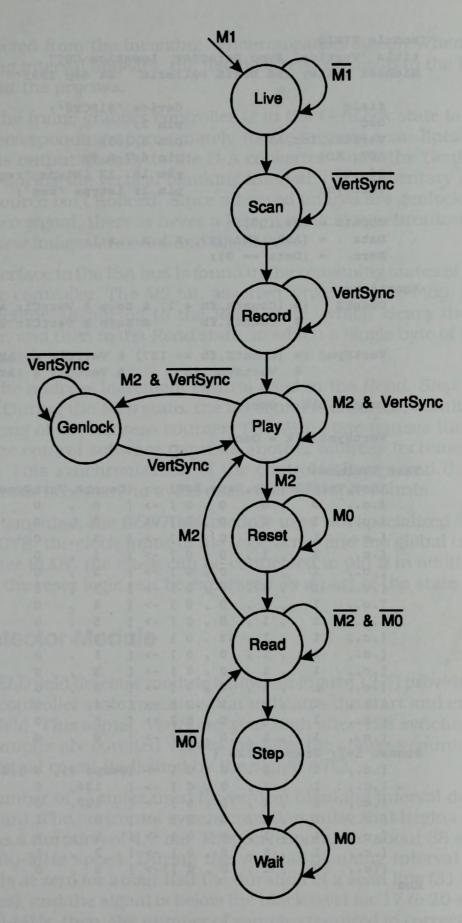

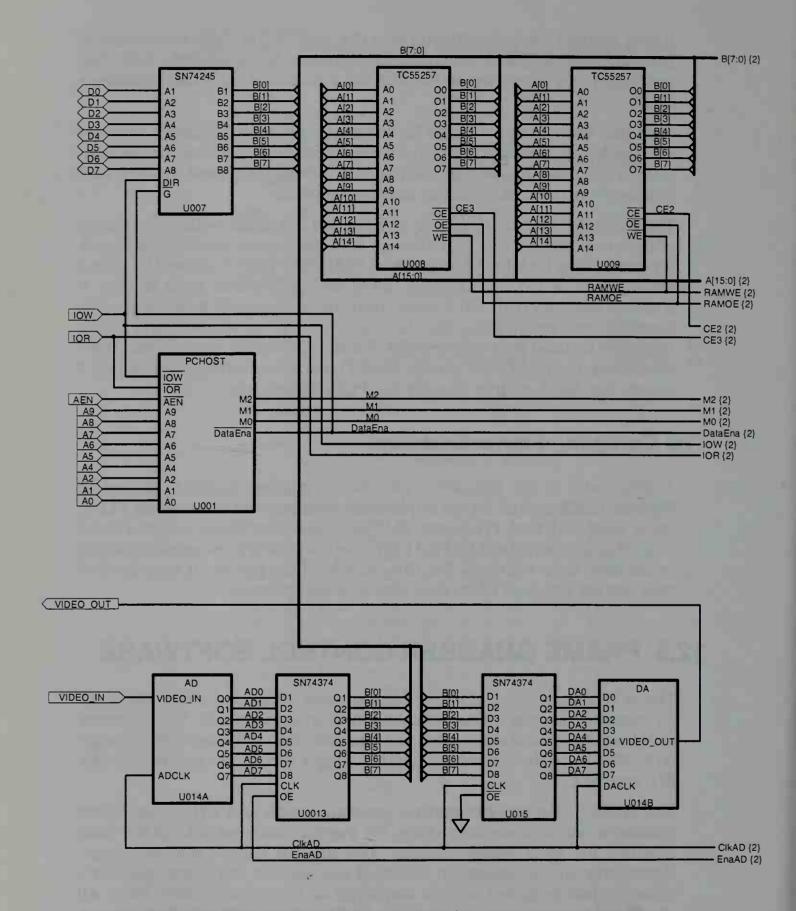

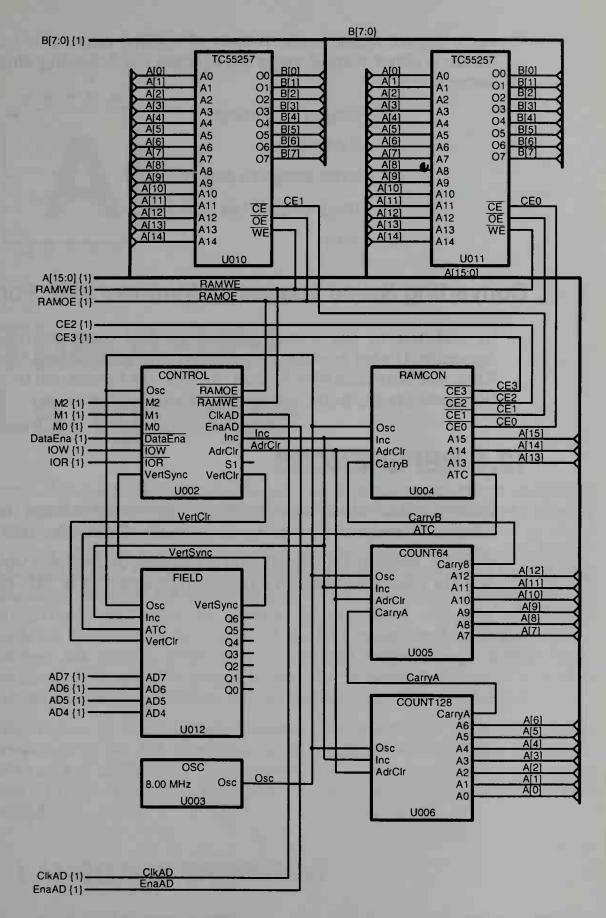

#### Chapter 12 A Video Frame Grabber, 203

- 12.1 GENERAL DESIGN REQUIREMENTS, 203

- 12.2 THE VIDEO FRAME GRABBER SYSTEM. 207

- 12.3 FRAME GRABBER CONTROL SOFTWARE, 221

#### 12.4 REFERENCES, 224

#### Appendix A The ABEL Language, 225

A.1 LANGUAGE OVERVIEW. 225

A.2 DECLARATIONS, 228

A.3 EXPRESSIONS, 236

A.4 EQUATIONS, 250

A.5 STATE DIAGRAMS, 256

A.6 TRUTH TABLES, 262

A.7 TEST VECTORS, 265

A.8 MACROS, 266

A.9 DIRECTIVES, 268

A.10 REFERENCES, 278

#### Appendix B The ABEL Software, 279

#### Appendix C Mach 215 Special Device Information, 283

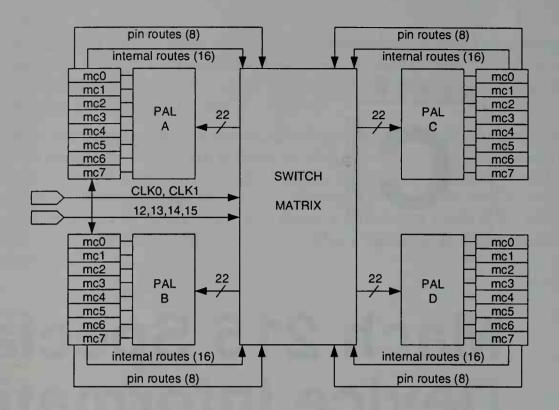

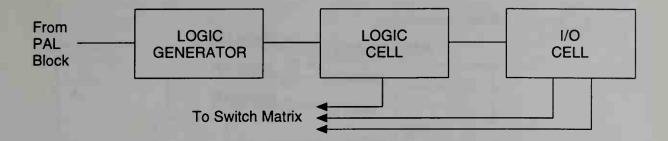

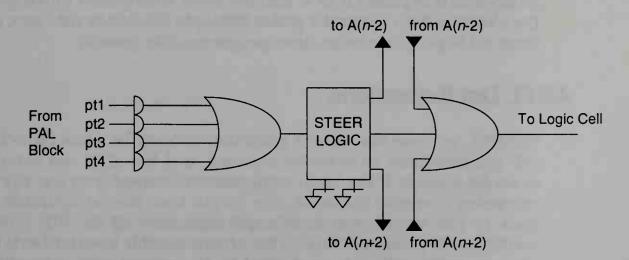

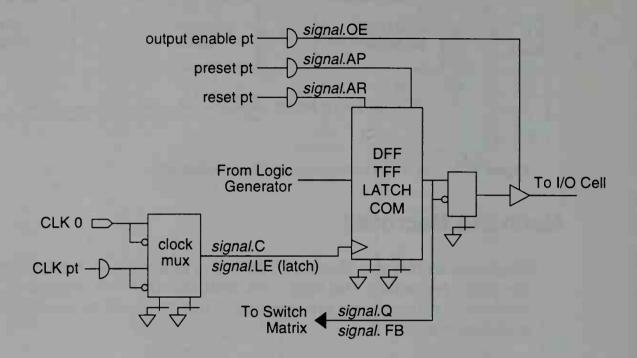

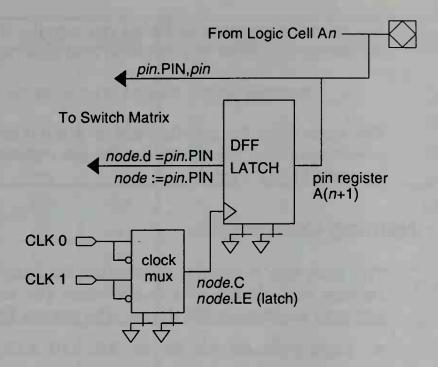

C.1 MACH 215 DEVICE ARCHITECTURE, 283

C.2 DESIGN STRATEGIES. 288

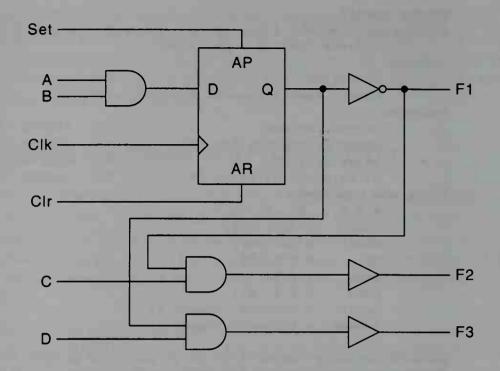

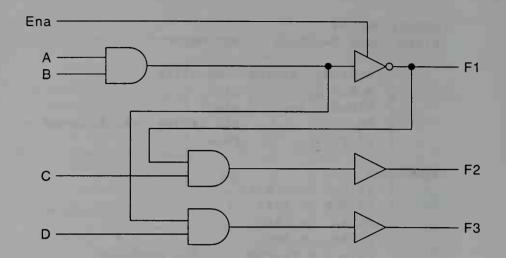

C.3 DESIGN EXAMPLES, 293

C.4 REFERENCES, 306

#### Appendix D Supplementary Listings for Chapter 12, 307

VFG.C. 307

VFG2BMP.C. 309

Index, 315

# **Preface**

ABEL (Advanced Boolean Expression Language) was introduced by Data I/O Corporation in 1984 and is now used by tens of thousands of digital circuit designers worldwide. The ABEL language was designed to allow small to medium-sized circuits (ranging in size from a few logic gates up to circuits composed of many thousands of gates) to be described and implemented in programmable logic devices (PLDs).

PLDs have become extremely common in modern digital systems, and the increasing popularity of these devices has led to an explosion of new device architectures. In addition, the densities of the newest devices have made it impractical to attempt a complex PLD-based design without design entry software. ABEL allows you to quickly and efficiently create large designs and to use one design description method for virtually all PLDs available.

Digital Design Using ABEL leads you through the basics of HDL-based digital design and provides dozens of examples of how ABEL can be used for digital applications. One primary reason for ABEL's popularity is its simplicity. While more complex and universal hardware description languages (such as VHDL and Verilog) may become more widely used design languages at some point in the future, these languages are primarily intended for circuit modeling, rather than for general-purpose logic design. ABEL, on the other hand, was designed specifically for the purpose of describing digital circuits for implementation in programmable logic. This specific purpose has made it possible to keep the language relatively simple and easy to use and makes ABEL a good language for learning concepts of HDL-based design.

The book begins with a discussion of the fundamentals of digital design, with special emphasis placed on techniques that are appropriate for users of ABEL. Chapters 1 through 4 cover topics such as Boolean algebra, logic minimization, and sequential circuit design and help the reader to better understand how traditional digital design techniques are applied, as well as shedding light on the processing and optimizations that are performed by the ABEL design software. Chapter 5 introduces the ABEL language and shows by example how the various forms of description (equations, truth tables, and state diagrams) are used to describe circuits at a high level.

In the second half of the book, beginning with Chapter 6, we provide examples of logic circuits and complete designs that have been described using the ABEL language. These chapters describe a variety of common digital circuits, which range from simple decoders and comparators to more complex sequential circuits such as counters and shift registers. You can use these common circuits as building blocks for larger applications. Armed with the information presented in these chapters, it will be possible for you to describe circuits ranging from simple combinational functions to complex state machine applications consisting of hundreds, or even thousands, of equivalent TTL gates. In the final chapter we describe a complex application that has been developed using ABEL.

Appendix A serves as a complete ABEL language reference and includes a wealth of information useful for new ABEL users. This appendix also contains additional information (including information not found in the standard ABEL documentation) useful to those who already have some experience with the ABEL language.

The software included with *Digital Design Using ABEL* is a device-limited subset of ABEL version 5.0. The software includes all features necessary to enter, compile, simulate, and fit designs using a variety of widely available programmable logic devices. These devices range from simple PAL-type devices like the 16L8, 16R4, 16R6, and 16R8 to more complex PLDs with configurable macrocell logic, including the PEEL 18CV8, Altera EP320 EPLD and AMD Mach 215 complex PLD. With this software it is possible for you to create, optimize, and simulate logic circuits that would be difficult or impossible to optimize using traditional methods of design.

Digital Design Using ABEL incorporates a great deal of material from an earlier book by the authors, *Practical Design Using Programmable Logic* (Prentice Hall, 1991). Readers who are interested in learning more about programmable logic devices, their history, architectures, and applica-

tions, are encouraged to consult *Practical Design Using Programmable Logic*.

This book would not have been possible without the support of many people. We would especially like to thank our colleagues at Data I/O Corporation and the many ABEL users who have contributed, through their questions and comments, to the information presented here. We would also like to thank Mark Sasten for his careful review of the manuscript.

This book would not be complete without the ABEL software. Bob LaTurner burned the midnight oil to create the customized version of ABEL included with the book, and his efforts are greatly appreciated. Special thanks also go to Karen Gettman at Prentice Hall for her support and encouragement.

David Pellerin Michael Holley The state of the s

# Introduction

ABEL (Advanced Boolean Expression Language) is a design language and set of supporting software programs that allow complex logic designs to be entered, compiled, optimized, simulated, and then implemented in programmable logic. ABEL is a device-independent language, meaning that a design written in ABEL does not have to explicitly state what device or technology will be used for implementation. The language does, however, include many features and constructs that give you control over a variety of device-specific circuit elements. In this book we concentrate on the device-independent aspects of ABEL and point out device-specific features or design requirements as needed.

#### 1.1 DESIGN ENTRY USING ABEL

ABEL provides three different design representations that you can combine as needed to completely specify a design. These representations are equations, truth tables, and state diagrams. ABEL also provides a test vector language that can be used to describe circuit stimulus and expected outputs for simulation. A sample ABEL source file is shown in Figure 1.1. This source file describes an eight-state counter using equations. (This and other counters are described in Chapter 7.)

Equations are most useful when the design to be described has some underlying pattern or regularity. Multiplexers, shift registers, and counters are all examples of circuits that have these attributes. ABEL

```

module count256

title '8-bit counter'

// 8-bit counter with hold and synchronous reset. //

// Appropriate for most PLD architectures.

clock, reset, hold pin;

q7..q0

pin istype 'reg';

Count = [q7..q0];

equations

Count.clk = clock;

Count := !hold & (Count.fb + 1) & !reset

# hold & Count.fb & !reset;

test_vectors([clock,reset,hold]->Count)

[.c., 1 , x.]-> 0;

0

0 ]->

[ .c. ,

1:

0

0 ]->

.c.,

2:

0 1->

.c. ,

0

4:

, 1]-> 4;

.c. ,

0

.c. ,

0

1 ]->

.c. ,

0

0 , 0 ]->

.c. ,

0 , 0 ]->

.c. ,

7;

.c. ,

0 , 0 ]->

8;

[.c., 0 , 0]->

9;

0

0 ]-> 10;

.c. ,

end

```

Figure 1.1 ABEL source file for 8-bit counter

raises the level of design abstraction for circuits such as these by incorporating high-level equation features such as sets, arithmetic operators, and relational operators. These features allow far more abstract forms of expression than are possible using simple sum-of-products Boolean equations.

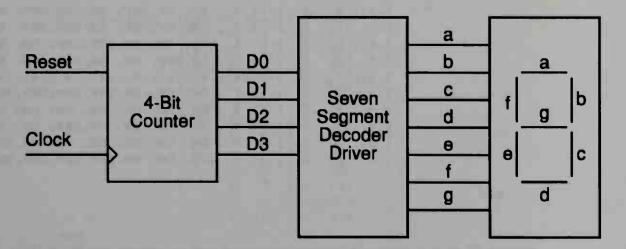

Truth tables are most useful for designs that have no underlying pattern or order. A typical example of such a circuit is a decoder for a seven-segment display such as the one shown in Figure 1.2. (This design is described in more detail in Chapter 5.) The truth table is a natural way to describe partially specified functions in which there are don't-care conditions. Truth tables are also a convenient way in which to describe the behavior of sequential circuits that contain a large number of similar

```

module BCD7

title 'BCD to 7-segment display driver'

// Seven-segment display driver with active-low

11

// outputs. Segments:

11

b

11

11

11

11

-a-

11

C

11

pin;

"BCD input

a,b,c,d,e,f,g pin istype 'dc,com'; "Segment outputs

pin;

"Output enable

= [D3..D0];

= [a,b,c,d,e,f,g];

LED

ON, OFF = 0, 1;

"Inverted sense

equations

LED.oe = !OE;

"Define output enable

truth_table(BCD->[ a , b , c , d ,

f,

0 -> [ OFF, OFF, OFF, OFF, OFF,

1 -> [ ON, OFF, OFF, ON,

ON,

ON,

2 -> [ OFF, OFF, ON, OFF, OFF,

ON, OFF];

3 ->[ OFF, OFF, OFF, OFF,

ON,

ON, OFF];

4 \rightarrow [ ON, OFF, OFF, ON,

ON, OFF, OFF];

5 -> [ OFF, ON, OFF, OFF, ON, OFF, OFF];

6 ->[ OFF,

ON, OFF, OFF, OFF, OFF];

7 -> [ OFF, OFF, OFF, ON, ON, ON, ON];

8 -> [ OFF, OFF, OFF, OFF, OFF, OFF];

9 -> [ OFF, OFF, OFF, OFF, ON, OFF, OFF];

test_vectors

([OE,BCD]->[ a, b, c, d, e, f, g])

[ 0, 0 ]->[ OFF, OFF, OFF, OFF, OFF, ON];

[ 0, 1 ]->[ ON, OFF, OFF, ON,

ON, ON,

[ 0, 2 ]->[ OFF, OFF, ON, OFF, OFF, ON, OFF];

[ 0, 3 ]->[ OFF, OFF, OFF, ON, ON, OFF];

[ 0, 4 ]->[ ON, OFF, OFF, ON, ON, OFF, OFF];

[ 0, 5 ]->[ OFF, ON, OFF, OFF, ON, OFF, OFF];

[ 0, 6 ]->[ OFF, ON, OFF, OFF, OFF, OFF];

[ 0, 7 ]->[ OFF, OFF, OFF, ON, ON, ON];

[ 0, 8 ]->[ OFF, OFF, OFF, OFF, OFF, OFF];

[ 0, 9 ]->[ OFF, OFF, OFF, OFF, ON, OFF, OFF];

[ 1, 5 ]->[ .z., .z., .z., .z., .z., .z., .z.];

end

```

Figure 1.2 Seven-segment display driver design file

state\_diagram BCD

State Zero: C4 = 0;

If Cin Then One Else Zero;

State One: C4 = 0;

If Cin Then Three Else Two;

State Two: C4 = 0;

If Cin Then Five Else Four;

State Three: C4 = 0;

If Cin Then Seven Else Six;

State Four: C4 = 0;

If Cin Then Nine Else Eight;

State Five: C4 = 1;

If Cin Then One Else Zero;

State Six: C4 = 1;

If Cin Then Three Else Two;

State Seven: C4 = 1;

If Cin Then Five Else Four;

State Eight: C4 = 1;

If Cin Then Seven Else Six;

State Nine: C4 = 1;

If Cin Then Nine Else Eight;

Figure 1.3 ABEL state diagram language

state transitions. Truth tables for these applications will be explored in Chapter 11.

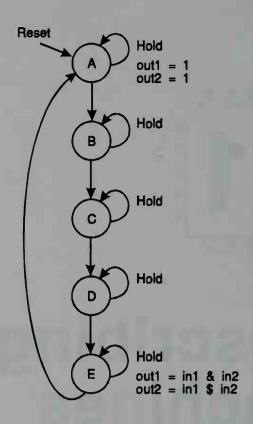

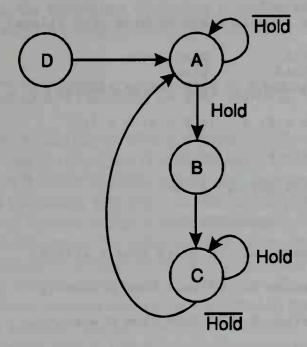

ABEL's state diagram language can be used to describe the behavior of finite state machines (FSMs). The choice of whether to use state diagrams, equations, or truth tables for descriptions of these circuits is largely a matter of personal taste. State diagrams tend to be more lengthy than equivalent truth table descriptions, but are usually more readable if there are a large number of states. Figure 1.3 is an excerpt from a serial BCD (binary coded decimal) decoder presented in Chapter 10.

```

Simulate ABEL 5.03e Date: Fri Sep 10 18:10:27 1993

Fuse file: 'fib1.tt1' Vector file: 'fib1.tmv' Part: 'PLA'

CC

1 1

7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0

V0001 C 1

LLLLLLLLLLLLLLLLLLLLLL

V0002 C 0

LLLLLLLLLLLLLLHLLLLLH

V0003

V0004 C 0

LLLLLLLLLLLLLLLLLLLLLLLLLLL

C 0

LLLLLLLLLLLLLLLLLLLLL

V0005

LLLLLLLLLLLLHHLLLLH

V0006 C 0

LLLLLLHHLLLLLHLHLLLLLLLL

V0007

C 0

C 0

LLLLLHLLLLLLLLLLLLLLHLLH

V0008

LLLLHLLLLLLHHLLLLHLHLH

V0010 C 0

LLLLHHLHLLLHLHLLLLLLLL

V0011 C 0

LLLHLHLLLLLLLLLLLLHLLHH

V0012 C 0

LLHLLLLLHHLHHLHHLHLHLLH

V0013 C 0

LLHHLHHHLHLHHLLHHLLHLLLL

V0014 C 0

LHLHHLLHHLLLLLLHHHLLLL

HLLHLLLHHHLLLHLHHHHLLH

V0015 C 0

V0016 C 0

V0017

C 0

V0018 C 0

LLLLLLLLLLLLLLLLLLLLLL

V0019 C 0

LLLLLLLLLLLLLLHLLLLLLH

20 out of 20 vectors passed.

```

Figure 1.4 Sample ABEL simulation results

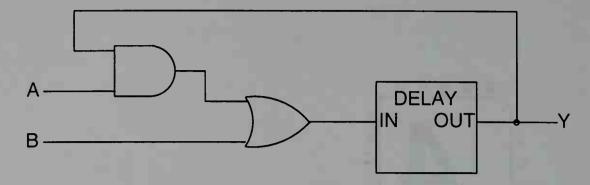

#### **Test Vectors and Simulation**

Test vectors are lists of values representing inputs and corresponding outputs of the design while under test. In ABEL, test vectors are entered into source files as an integral part of the design. The ABEL test vector language is virtually identical to the ABEL truth table language and is used to describe test stimulus and expected outputs for simulation. The ABEL logic simulator that is provided with this book can be used to check the function of a design before moving into the implementation phase. Figure 1.4 shows a sample output from the ABEL simulator.

#### **Logic Synthesis**

Logic synthesis is the process of converting a circuit description into a form appropriate for hardware implementation and optimizing that description to create a physical circuit that meets specific constraints. The constraints that drive logic synthesis may be weighted and may

include such things as the total circuit size, operating speed, power usage, or testability. Device-specific synthesis constraints may include such things as primitive libraries, fan-in and fan-out restrictions, and device resource constraints. The actual device mapping process may include logic partitioning, resource allocation, placement and routing, and other functions.

Logic minimization and multilevel logic optimization are specific logic synthesis features that are covered in this book. The software provided with this book includes logic minimization (based on the Espresso optimization software developed at the University of California at Berkeley), but does not include the more advanced logic synthesis features required to implement designs in the most advanced complex PLDs and FPGAs (field programmable gate arrays).

When high-level design methods are used, effective logic synthesis techniques are the key to a successful and efficient final circuit. It is logic synthesis that allows designs to be described at a higher level of abstraction. Since the goal of logic synthesis is to translate a circuit representation into a form that meets the specified constraints of the design, it's important to decide what constraints are most important for each design.

For most designs being implemented with programmable devices, the most direct constraints are related to the restricted architectures of the devices. Automated logic synthesis tools that help to optimize combinational circuits for various global cost and operational constraints have existed for some time. Automated tools that help with logic synthesis for constrained architectures, however, have only recently appeared. These device-specific tools, called *fitters*, are the key to efficient implementation of device-independent designs.

Logic synthesis features available in today's design tools are certainly useful for that part of the design process in which logic synthesis can benefit. It's important to realize, however, that the currently available synthesis tools, no matter how highly automated or tightly integrated, cannot be used without an awareness of their limitations. Specifically, you must always be aware of how basic design decisions can affect the final circuit produced by the tools. Automated logic synthesis tools can only help to optimize a logic design as you have specified it. They cannot explore design-level alternatives and make intelligent decisions about those alternatives. In later chapters, we'll explore some of these design-level optimizations and alternatives.

#### **Implementation Considerations**

All potential implementation technologies (TTL, PLD, FPGA, or ASIC) have their strengths and weaknesses, and it is important to keep these strengths and weaknesses in mind when creating a new design. Since most ABEL designs are eventually implemented in PLDs and FPGAs, these are the technologies that we will concentrate on.

PLDs and FPGAs are devices with constrained architectures. While the specific constraints may differ from one device family to another, the existence of these constraints leads to limitations in the size and configuration of the circuits that can be implemented in them. While automated design tools can help in the conversion of abstract, device-independent design concepts into working circuits, the designer must still understand the basic limitations of the target technology. By showing how the most common constraints effect the implementation of relatively simple circuits, we'll be able to demonstrate some of the many design trade-offs that are required for larger designs and other technologies.

# Combinational Circuits

A solid understanding of digital logic fundamentals is critical to the understanding of ABEL and the high-level design capabilities that it provides. In this chapter, we'll review these fundamentals and examine how the techniques of digital logic design can be used to help us design at a higher level. From there we'll move quickly into advanced topics that are particularly important for ABEL users to understand.

The terminology of digital logic can be confusing. Therefore, a major goal of this chapter is to define the language of logic design as used in this book. Even if you are a seasoned logic designer, bear with us during the early parts of this discussion so that we can make sure that we are speaking a common language. This will be more important in Chapter 3, as we discuss specific logic optimizations that are performed by the ABEL software, as well as those that must be performed manually.

#### 2.1 LOGIC CIRCUITS AND LOGIC FUNCTIONS

First, we will try at all times to distinguish between real circuits and purely functional representations of these circuits. In the following discussions, we will consider a logic function to be an abstract concept, whereas a logic circuit is a collection of physical circuit elements and interconnections (typically wires or metal traces). Logic circuits have

real-world attributes, such as size, speed, and critical timing relationships. This distinction is important to us because, when designing with ABEL, we are designing at a higher functional level, rather than at a real implementation level. As we'll see, though, the form of the implementation and the constraints of the target architecture must frequently be considered even when designing at a high level.

#### **Basic Logic Gates**

Logic gates are the basic building blocks of digital logic circuits. A logic gate may be thought of as a decision-making element. A logic gate has one or more inputs (each of which can be either *true* or *false* at any given time) and a single output that produces either a true or false value based on the values of the gate inputs. To simplify later discussions, we may refer to the input and output values of these gates as either logic level 1 (true) or logic level 0 (false). The numerals 0 and 1, when used in this context, are not numbers; they are logic values.

The inputs and outputs of logic gates are called *signals*. In an actual hardware implementation, a signal corresponds to a wire or metal channel that carries current from one circuit element to another. For the moment, we can assume that all signals are, at any given time, either 0 or 1, with no ambiguous signal values. When one or more logic gates are connected together and the input and output signals are given some significance (usually indicated by specific signal names), they form a logic circuit.

In describing the operation of logic gates and logic circuits, it is common to use a form of representation known as the *truth table*. A truth table simply associates combinations of inputs with resulting outputs. Truth tables can be used to fully specify a logic function (as in the following examples) or to partially specify it. We'll use fully specified truth tables to define the basic logic gates. Advanced applications of fully and partially specified truth tables will be covered later.

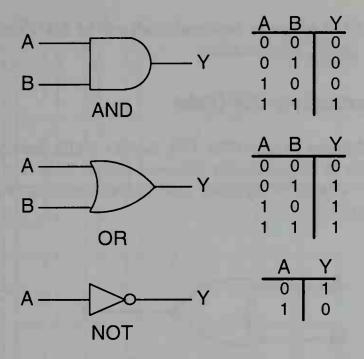

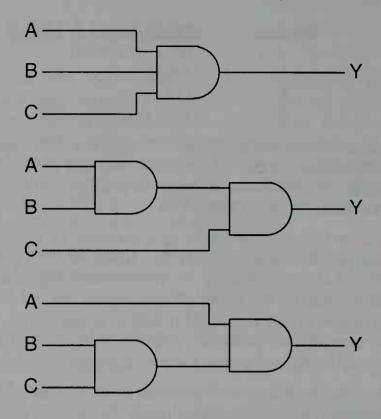

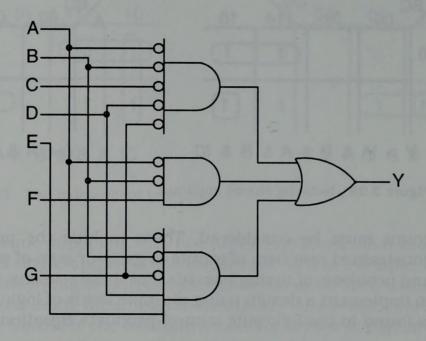

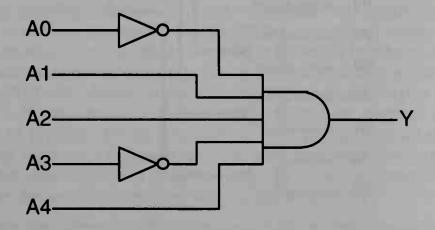

The logic gates of most interest to us for Boolean logic manipulations are the AND, OR, and NOT (inverter) gates. The most common symbolic representations of these gates is shown in Figure 2.1, along with truth tables describing their operations.

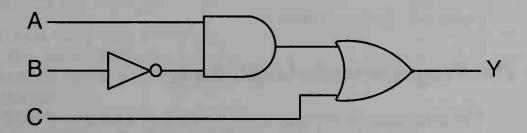

The AND, OR, and NOT gates are analogous to the words "and," "or," and "not" in the English language. We could describe a logic function using the english language. For example, we might say "The function Y shall be true when the input signal A is true and the input signal B is not true, or when the input signal C is true." If we wanted to build a

Figure 2.1 Basic gates

circuit that implemented this function, it might look like the circuit shown in Figure 2.2.

This logic circuit is what is known as a combinational logic circuit. This means that, for any set of input values (as shown in a fully specified truth table) there is one and only one possible circuit output value, regardless of the previous state of the circuit. By gluing together an appropriate collection of ANDs, ORs, and NOTs, it is possible to implement any combinational logic function.

There are, of course, other types of logic gates. Designers who are used to constructing circuits out of standard TTL gates or to designing circuits using "bubble logic" techniques are often more comfortable with NAND or NOR gates. These gates are widely used because they normally require less transistor circuitry for implementation than do ANDs and ORs. For our purposes, however, it is more convenient to consider NAND

Figure 2.2 A simple logic circuit

and NOR gates to be combinations of AND and NOT gates or OR and NOT gates, respectively.

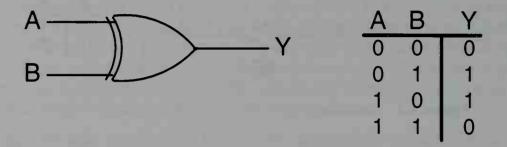

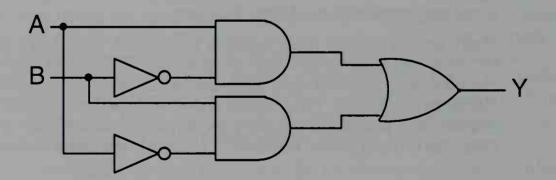

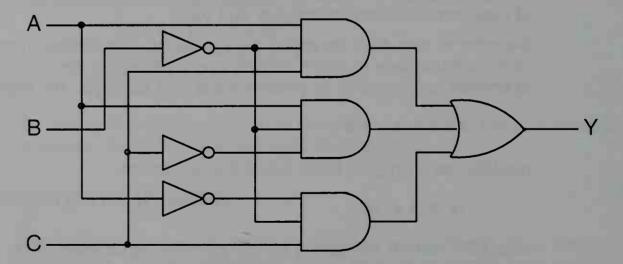

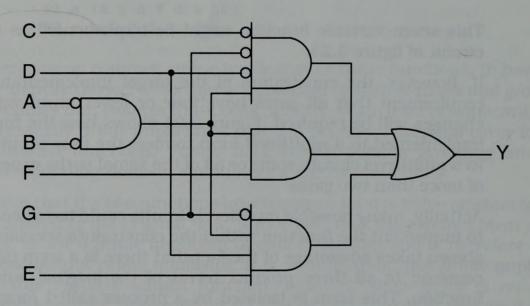

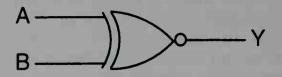

#### The Exclusive-OR Gate

In addition to the AND, OR, NAND, NOR, and NOT gates, another type of gate is of particular interest to us. This is the *exclusive-OR gate*, or *XOR*. The XOR symbol and corresponding truth table are shown in Figure 2.3.

Figure 2.3 Exclusive-OR (XOR) gate

Like NAND and NOR gates, the XOR can be constructed from the basic AND and OR gates, as shown in Figure 2.4. We'll discuss how the XOR gate can be used to advantage later in this chapter.

Figure 2.4 Exclusive-OR circuit

#### The Programmable Logic Array

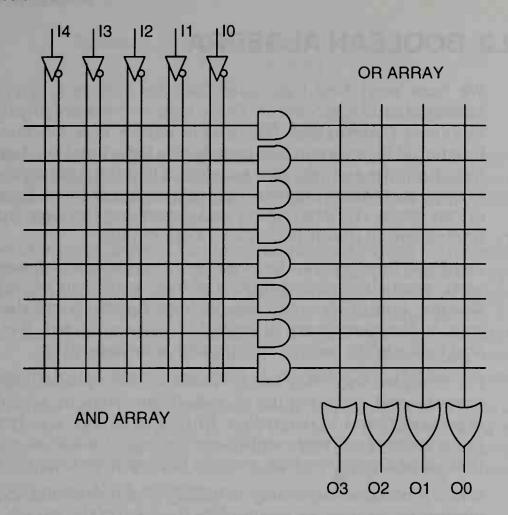

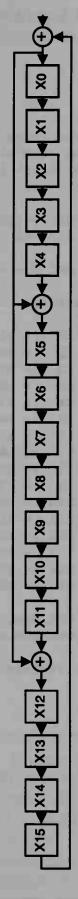

The programmable logic array, or *PLA*, is a matrix of NOT, AND, and OR gates arranged as shown in Figure 2.5. The diagram is simplified by combining all the inputs to each AND and OR gate into a single line.

Figure 2.5 Programmable logic array

The actual number of signals feeding each gate can be determined by counting the number of intersections on the line.

Each intersection of a vertical and horizontal line represents a potential interconnect point. There are two arrays of possible interconnects in a PLA. The upper array is the AND array, while the lower is the OR array.

The simple PLA shown in the figure has five inputs, each of which is available to the AND array either directly (its *true* value) or through an inverter (its complement). The AND gate outputs are fed into the OR array, so any AND gate output can be used as an input to any OR gate.

The PLA structure is important to us because it is the basis for nearly all the programmable devices currently in use, and it is the basic structure assumed by ABEL and used as an internal design representation.

#### 2.2 BOOLEAN ALGEBRA

We have seen how logic gates can be arranged to create a simple combinational logic circuit. These logic circuits are physical implementations of *Boolean logic functions* or simply *logic functions*. Every combinational logic circuit has exactly one logic function, but for any given logic function an unlimited number of logic circuits can be constructed to implement that function. The logic design process, then, is composed of two steps: (1) determining and describing the logic function and (2) implementing that function as a logic circuit.

Any logic function can be expressed in a number of ways. As we have seen, symbolic representations of logic gates can be used to describe circuits, and in fact most simple logic functions are described in this way. In the case where discrete TTL gates are used, the logic function and logic circuit may be determined simultaneously.

For complex logic functions, however, the optimal logic circuit isn't obvious and may require a significant amount of calculation and experimentation to determine. In this situation, it is beneficial to use more conceptual representations for logic functions, representations that allow alternative logic circuits to be quickly identified and selected.

When it becomes necessary to modify a logic function, experiment with alternative circuits, or manipulate the form of the circuit, these conceptual forms of representation are usually more helpful. We have seen how truth tables, and even English language statements, can be used to describe the operation of a digital logic function in a conceptual way. Another form of representation, *Boolean algebra*, has been used for many years to describe and manipulate logic functions.

Boolean algebra is a system of mathematics that allows us to manipulate logic. As before, we use the value 1 to indicate the true logical value and a 0 to indicate the false logical value. We'll use true/false and 1/0 values interchangeably in the remaining discussions.

#### **Boolean Equations**

At the heart of Boolean algebra are the Boolean operators. These operators correspond to the AND, OR, XOR, and NOT logic gates presented earlier. There are many ways of representing the AND, OR, NOT, and XOR Boolean operators, and a variety of different representations are used in digital design languages and formal texts. In ABEL and in this book, we use the following symbols for Boolean operations:

| Symbol | Description        |

|--------|--------------------|

| !      | NOT (inversion)    |

| &      | AND                |

| #      | OR                 |

| \$     | XOR (exclusive-OR) |

In most formal texts on logic design, the AND operator is omitted from Boolean equations. In this book, we will at all times include the AND operator in equations in order to remain consistent with ABEL-related discussions in other chapters.

Operator precedence (*order of evaluation* or *binding*) is the order shown in the preceding list. (In ABEL, however, the OR and XOR operations have equal precedence.) As in standard algebra, parentheses may be used to change the order of operations. In Boolean algebra, a variable is a named entity (corresponding to a signal in a logic circuit) that can have one of two possible values: 1 or 0. A Boolean *expression* is a grammatically correct sequence of variables and Boolean operators.

A Boolean equation is composed of an output variable that is assigned a Boolean logic function through the use of the assignment operator, which is the equals sign. In ABEL, each equation is terminated by a semicolon. The AND, OR, XOR, and NOT gates can be represented by the following ABEL equations:

```

Y_AND = A & B;

Y_OR = A # B;

Y_XOR = A $ B;

Y NOT = !A;

```

To help clarify these concepts, consider the following Boolean equation:

```

Y = A & B # C & !B;

```

This Boolean equation describes a logic function of three input variables (Y = f(A, B, C)). The function can be described by the following English language statement: "The output variable Y shall be true if the input variables A and B are both true, or if the input variable C is true and the input variable B is false."

The NOT operator is a unary operator, which means it operates on a single variable or subexpression. The NOT operator creates the complement (inverted) value of a variable or subexpression. For Boolean algebra purposes, it is often most convenient to consider a true variable and the complement of that variable as two separate entities. When this is done, we refer to the inputs as literals. In the Boolean equation we just presented, for example, the variable *B* appears as both a true and

Figure 2.6 Three possible implementations of the same logic function

complemented variable. This means that the equation contains four distinct literals (A, B, !B,and C).

The AND, OR, and XOR operators are binary operators, operating on two variables or subexpressions. Actually, it is sometimes more convenient to consider the AND and OR operators to be n-ary operators (operators that can operate on more than two variables) since the actual logic gates that correspond to these operators may have more than two inputs. This is allowed by the associative laws for these operators, as we'll see in a moment.

Boolean algebra is a convenient method with which to describe logic functions. It is never possible, however, to completely specify a logic circuit with Boolean algebra, since there are many possible circuit interpretations of a Boolean equation. This is shown in Figure 2.6. Each of the three circuits shown will have subtly different operating characteristics, due to signal propagation and gate switching delays.

#### Formal Rules for Boolean Operations

A number of operations are used in the manipulation of Boolean equations. We will present the formal rules of the operations most useful to logic designers, although complete descriptions and proofs of these

are beyond the scope of this book. The interested reader is referred to any one of a number of books on the subject of logic design for further study. Some of these texts are listed in the references at the end of this chapter.

The following is a list of the operations that are of greatest interest to us. We have added some exclusive-OR operations to the standard operations commonly presented. We will assume the validity of these additional operations without formal proof.

#### **Standard Operations**

- 1. Commutative laws:

- (a) A # B = B # A

- (b) A & B = B & A

- 2. Identities:

- (a) A # 0 = A

- (b) A # 1 = 1

- (c) A & 0 = 0

- (d) A & 1 = A

- 3. Complement identities:

- (a) A # !A = 1

- (b) A & !A = 0

- 4. Involution:

- (a) !!A = A

- 5. Indempotence:

- (a) A # A = A

- (b) A & A = A

- 6. Distributive laws:

- (a) A # (B & C) = (A # B) & (A # C)

- (b) A & (B # C) = (A & B) # (A & C)

- 7. Associative laws:

- (a) A # (B # C) = (A # B) # C

- (b) A & (B & C) = (A & B) & C

- 8. Absorption:

- (a) A # (A & B) = A

- (b) A & (A # B) = A

- (c) A # (!A & B) = A # B

- (d) A & (!A # B) = A & B

- 9. Unity:

- (a) A & B # !A & B = B

- (b) (A # B) & (!A # B) = B

#### **Exclusive-OR Operations**

- 10. Associative law:

- (a) A \$ (B \$ C) = (A \$ B) \$ C

- 11. Distributive law:

- (a) A & (B & C) = A & B & A & C

- 12. Commutative law:

- (a) A \$ B = B \$ A

- 13. XOR identities:

- (a) A \$ 1 = !A

- (b) A \$ 0 = A

- (c) A \$ A = 0

- (d) A \$ !A = 1

- 14. Rules of XOR complement:

- (a) !(A \$ B) = A \$ !B

- (b) !(A \$ B) = !A \$ B

- (c) A \$ B = !A \$ !B

In addition to these rules, two theorems are widely used in Boolean equation manipulations and logic minimization.

#### **DeMorgan's Theorem**

*DeMorgan's theorem* is used to find the complement of a Boolean expression. This is particularly useful for programmable logic applications:

DeMorgan's theorem can be generalized as follows: The complement of any Boolean expression can be determined by replacing each OR operator with an AND operator (while preserving the order of evaluation), replacing each AND operator with an OR operator, and replacing each literal with its complement. For example, the following two relationships are valid:

#### **Shannon's Expansion Theorems**

Shannon's theorems are used to isolate (factor out) one or more variables in a logic function. Shannon's expansion theorems may be described by the notation:

(a)

$$f(A,B,C,...) = A & f(1,B,C,...) # !A & f(0,B,C,...)$$

(b)  $f(A,B,C,...) = (A # f(0,B,C,...)) & (!A # f(1,B,C,...))$

where f(A,B,C,...) represents any multiple-variable Boolean logic function. Shannon's theorems are particularly useful during multilevel logic minimization.

#### **Standard Forms for Boolean Logic**

A number of general forms may be used to express a Boolean logic function. An understanding of these forms is important for effective use of logic minimization techniques and tools.

We refer to any AND operation as a product. Any Boolean expression that contains one or more literals operated on by one or more AND operators is referred to as product term. For example, the expression

qualifies as a product term, while the expression

does not, since it includes a binary operator other than AND.

A product term expression is distinguished by the fact that only one set of input conditions will result in a true evaluation of the expression.

#### **Logical Sum**

OR operators are referred to as sums. Any Boolean expression that contains one or more literals operated on by one or more OR operators is a sum. The expression

!A # B # !C # D

is an example of a sum.

#### **Sum of Products**

When two or more product terms are operated on by one or more OR operators, the form of the resulting expression is *sum of products*. If we add an assignment operator and an output variable, we have a *sum of products Boolean equation*, as in the following ABEL equation:

Y = A & !B & C # A & !B & !C # !A & !B & C;

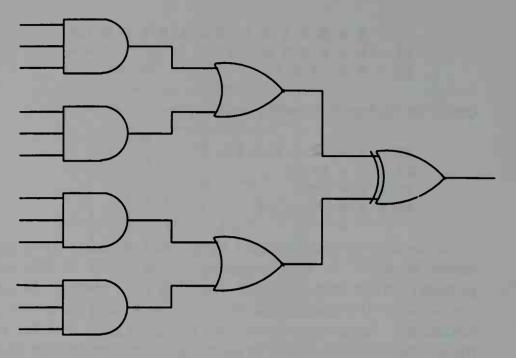

Expressed as logic gates, this expression could be composed of one 3-input OR gate fed by three 3-input AND gates. As Figure 2.7 shows, a sum-of-products form requires two levels of logic gates (discounting the NOT gates required for the complemented input literals) for implementation. For this reason sum-of-products Boolean logic functions are often referred to as two-level logic functions.

The sum of products form is the basis for most logic optimization methods, and maps directly into the PLA structure presented earlier.

Figure 2.7 Sum-of-products two-level logic

By utilizing the laws and theorems presented earlier, it is possible to express any logic function, regardless of complexity, in sum-of-products form.

#### 2.3 USING BOOLEAN ALGEBRA IN ABEL

Using the basic laws and theorems presented as tools, we can now begin to experiment with various techniques that are useful for ABEL users. Many of these manipulations are performed automatically by the ABEL software, while others must be performed by the ABEL user. Chapter 3 describes in detail which optimizations are performed by the software provided with this book.

Before moving on, though, let's examine some of the reasons why these manipulations are often necessary. The primary motivations for Boolean logic manipulations are to reduce circuit size or improve circuit speed. All the common implementation technologies (simple and complex PLDs, FPGAs, and gate arrays) are constrained in some way. Most require that logic functions be implemented in specific forms (usually sum of products or some derivative of sum of products), and all have limited resources. The limiting resource is usually either logic gates or signal interconnections (routing).

Traditional PLDs, for example, are limited in the number of product terms that can be used for each output, so product term reduction is a primary goal of optimization for these devices. If a logic function can't be reduced sufficiently for a PLD implementation, it will be necessary to perform multilevel optimizations to spread the circuitry for that function across multiple levels of logic.

Another common limitation of PLDs is the number of inputs and outputs available in each device. If a design can't be implemented into a PLD due to I/O constraints, it is necessary to either change the design or choose a different implementation. Choosing a different implementation can involve using a different type of device, more than one device for the function, or an entirely different implementation technology.

Speed isn't generally much of an issue when you are dealing with a single PLD, since in most cases the delay times from inputs to outputs are fixed and predictable, and PLDs are available that are fast enough for most applications. For large designs implemented in FPGAs, or designs that utilize many PLDs, the delay of signals due to multiple levels of logic can wreak havoc on a system. For this reason more advanced multilevel logic optimizations may be needed for large designs.

#### 2.4 REFERENCES

Breeding, Kenneth J., Digital Design Fundamentals, Prentice Hall, Englewood Cliffs, NJ, 1989.

Mano, M. Morris, *Digital Design*, Prentice Hall, Englewood Cliffs, NJ, 1984.

Unger, Steven J., *The Essence of Logic Circuits*, Prentice Hall, Englewood Cliffs, NJ, 1989.

Wakerly, John F., Digital Design Principles and Practices, Prentice Hall, Englewood Cliffs, NJ, 1990.

# Logic Minimization

Logic minimization is the process of reducing the amount of circuitry required to implement a logic function. As we saw in Chapter 2, the optimal form of a logic circuit depends to a large extent on the architecture into which the logic function is to be implemented. There are dozens of methods for logic minimization and a wide variety of computer-based tools that utilize these methods. Although we can't hope to describe all these methods in this chapter, we will describe some of the more popular minimization methods and define some concepts common to all these methods.

Users of computer-based logic synthesis tools are often bewildered by the descriptions of algorithms and logic forms and the strange language used to describe the effectiveness of various techniques. The result, all too often, is that the users of these tools never really understand how to get the most benefit from them. In this chapter we'll go over some common logic minimization techniques and clear up some of the confusion over terminology.

## 3.1 TWO-LEVEL MINIMIZATION

To start with, consider a Boolean logic function with three variables A, B, and C. Each variable can be expressed as either its true or complemented value. If we enumerate all combinations of these three variables using the AND operator, we find eight possibilities, as follows:

!A & !B & !C !A & !B & C !A & B & !C !A & B & C A & !B & C A & !B & C A & !B & C A & B & C

Each of these eight expressions is referred to as a minterm, or canonical product. For any logic function of n variables, there are  $2^n$  possible minterms. These Boolean expressions are called minterms because, for each expression, there is only one set of input values that will result in the value 1. For example, the minterm !A & !B & C will only evaluate to 1 for one set of inputs (A, B, and C equal 0, 0, and 1, respectively). The importance of minterms lies in the fact that any logic function, regardless of complexity, can be expressed as a sum of one or more of its minterms.

## **Maxterms**

A *maxterm* is similar to a minterm, but is related to OR operations, rather than AND operations. The eight possible maxterms for three input variables are

!A # !B # !C !A # !B # C !A # B # !C !A # B # C A # !B # !C A # !B # C A # B # !C A # B # C.

These expressions are called maxterms because they will evaluate to a 1 for all but one possible set of input values.

## **Minsums**

A sum of products expression that consists of a sum of minterms is referred to as a minsum. This form is important for many logic minimization techniques and is sometimes referred to as the *canonical sum-of-products* or disjunctive normal form. For example, the 3-input sum-of-products expression

#### !A & B & C # A & !B & C # A & B & !C

is a minsum, since all the product terms in the expression are minterms, whereas the expression

#### !A & B & C # A & !B & C # B & !C

is not a minsum, since the product term B & !C is not a minterm (the variable A is not specified in the third product term).

## **Determining the Minsum of a Logic Function**

Any arbitrarily complex logic function can be converted to sum-of-products form. Furthermore, any logic function can be converted to its minsum form. To demonstrate how the minsum form of a logic function can be determined, consider the following expression:

#### A & !B & !C # A & B

To get this Boolean function into minsum form, we'll use the postulates and laws presented in Chapter 2. First, we know that the minsum form will require three input variables for each product term in the expression, so we use the identity postulate to get the intermediate form:

#### A & !B & !C # A & B & 1

Next, the complement postulate allows us to replace the 1 with the expression C # !C, resulting in

Finally, by utilizing the distributive law we obtain the minsum expression

### A & !B & !C # A & B & C # A & B & !C

## **Other Standard Forms**

There are other standard forms in which Boolean logic functions can be expressed, including the *product-of-sums canonical form* (referred to as the maxproduct form), but since the vast majority of devices are based on the sum of products form, and most logic minimization techniques are also based on sum-of-products, we won't dwell on these

other forms in this book. Again, the interested reader is referred to one of the many books written on the subject of digital logic design for further information.

## **Logic Minimization Methods**

The various Boolean logic manipulations that we have shown can be used to minimize logic. For large Boolean expressions, however, the most efficient approach to take using these manipulations typically isn't obvious, and finding the minimal solution can be extremely time consuming.

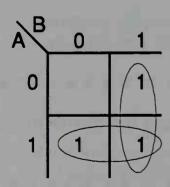

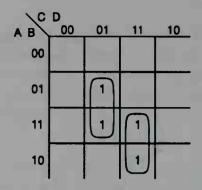

A common method for systematically determining the minimal sum-ofproducts expression for a given logic function was first described by Maurice Karnaugh in 1953. This method uses a symbolic representation of the logic function. The representation, called a Karnaugh map, graphically depicts the function in a modified form of truth table and allows simple, organized methods to be used for minimization.

To demonstrate how a Karnaugh map can be used, we will minimize the following logic function:

### A & B # !A & B # A & !B

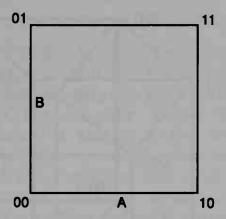

A two-variable Karnaugh map for this function is shown in Figure 3.1.

Figure 3.1 Two-variable Karnaugh map

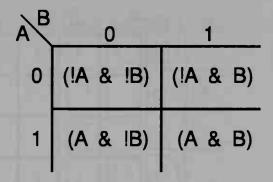

The Karnaugh map (which we will from now on refer to as a K-map) is composed of a number of boxes. Each box, or cell, represents one possible minterm for the function. Since this function has only two variables, there are  $2^2$  possible minterms, as described earlier. Each box is identified by the values indicated on the top and sides of the box; a 1 indicates the true asserted variable, whereas a 0 indicates the

Figure 3.2 Mapping minterms onto a 2-variable K-map

complement of that variable. In Figure 3.2, the possible minterms for a two-input Boolean function are shown in their corresponding K-map boxes.

If the minterm associated with a particular box actually exists in the minsum form of the Boolean expression, then a 1 is written in that box. The boxes so marked are referred to as *1-cells*. Cells not marked are called *0-cells*.

To minimize a function using a K-map, we utilize the following relationship developed from our earlier Boolean identities:

$$A & f0 # !A & f0 = f0$$

The variable *f*() represents any arbitrary Boolean function. To generalize this and apply it to the K-map: if there are two product terms and one is ANDed with a variable (*A*) while the other is ANDed with that variable's complement (*!A*), the product terms can be combined and the variable eliminated if the product terms are otherwise identical.

This situation is identified on the K-map by pairs of horizontally or vertically adjacent 1-cells. As Figure 3.1 shows, the pairs of 1-cells are grouped. Each group of two corresponding minterms can be combined into a single product term by elimination of the differing variable. For this expression, the two groupings result in the simpler sum A # B.

The K-map technique is a method for determining the minimal sum-ofproducts representation of a logic function from its minsum form. Most logic minimization algorithms, in fact, first determine the minsum form of a sum of products expression before beginning the minimization process.

If you examine the K-map layout, you will notice that moving one box either vertically or horizontally always results in a single bit change; in this case, either A or B changes, but never both. This is obviously the

Figure 3.3 Four-variable K-map

case for the simple two-variable K-map, but what about K-maps for larger numbers of variables?

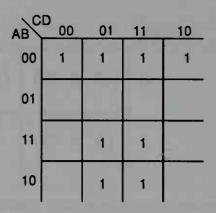

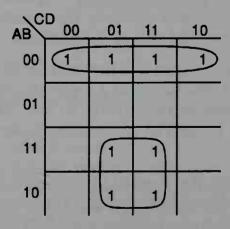

Figure 3.3 shows how a K-map for a four-variable Boolean function is written. This K-map is composed of 16 boxes, but is still two dimensional. Therefore, each box needs to represent the value of more than two variables as indicated in the numbering. To maintain the requirement of single bit changes between horizontally and vertically adjacent boxes, the horizontal and vertical axis values are numbered using a gray code (also called a reflected code). As in the two-variable K-map, each box represents a unique minterm. The rightmost box on the lower row, for example, represents the minterm A & !B & C & !D.

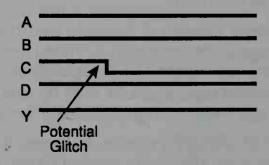

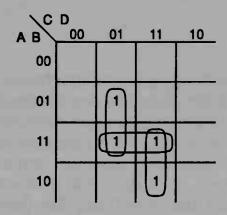

To reduce the four-variable minsum expression indicated in the figure, we first identify and circle all adjacent 1-cells. This is shown in Figure 3.4. Notice that, in the lower center of the K-map, there are four 1-cells grouped together in a square pattern. If these four were to be grouped as pairs, they could be combined in a number of ways. Which combination is appropriate? Actually, this decision isn't necessary. Whenever

Figure 3.4 Minimizing a logic function with a four-variable K-map

Figure 3.5 K-map for eight-minterm function

two pairs of 1-cells are adjacent in this manner, it's an indication that all four minterms can be combined into a single product term.

Similarly, the four 1-cells that form an encircled rectangle on the upper row can be combined, resulting in a significant reduction of logic. The completely minimized expression is

#### !A & !B # A & D

In this example, the variable *C* was completely eliminated.

Next, consider the expression and K-map of Figure 3.5. In this K-map, the eight 1-cells have been grouped into two squares. This is possible because the K-map edges are logically connected; it is convenient to think of the K-map in terms of a cylinder in both the horizontal and vertical directions. The variables *A* and *C* are both eliminated, and the minimized form of this expression is simply

B & !D # !B & D.

## **Using K-maps for Larger Functions**

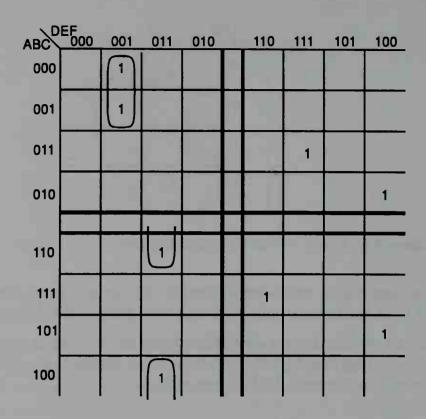

There are many more applications of K-map techniques that are of academic interest, but these are beyond the scope of this book. It is interesting to note however, that K-maps like the one shown in Figure 3.6 can be constructed to determine the minimized sum-of-products representation of expressions with more than four variables.

Since the size of the K-map increases exponentially with the increased numbers of variables, this method quickly becomes impractical for large designs. This fact and the availability of computer-based algorithms for logic minimization have for the most part eliminated the need for tedious manual K-map minimization. The K-map is useful, however, for graphi-

Figure 3.6 Six-variable K-map

cally demonstrating logic minimization concepts and gives important insights into the workings of computer-based logic minimization algorithms.

## Cubes

Another graphic representation that is useful for describing logic minimization concepts is the cube. Consider again the case where two minterms of a function differ only in the value of one variable, as in

#### !A & B & C # !A & B & !C

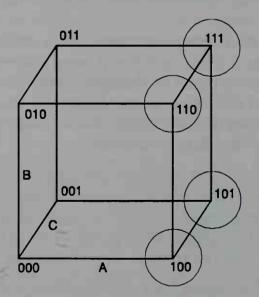

As we saw in the K-map discussion, the two minterms in this minsum can be represented by sequences of ones and zeroes that correspond to true and complemented input variables. Using this representation in another way, we can assign the minterms the values 011 and 010. A function of n variables has a total of  $2^n$  possible minterms. If we imagine that each variable corresponds to a dimension in space, we can represent the entire set of minterms as an n-dimensional cube.

Figure 3.7 shows a two-dimensional cube, or 2-cube, represented by four points connected by four line segments. This cube corresponds

Figure 3.7 Cube representation for two variables (2-cube)

Figure 3.8 Cube representation for three variables (3-cube)

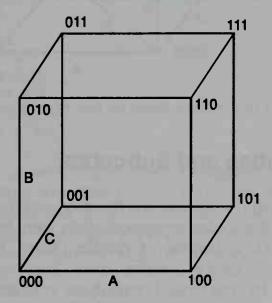

directly to its K-map representation; each point on the cube represents one box on a four-variable K-map. Movement along a horizontal line segment correspond to changes in the first variable, while movement in the vertical direction corresponds to changes in the second variable. Each point on the two-dimensional cube is labeled with the corresponding value of the input variables.

Figure 3.8 shows a three-dimensional cube, or 3-cube. The third dimension of this cube is drawn as diagonal line segments. Motion along these line segments corresponds to changes in the third variable. Notice that, no matter what line segment you are on, movement from one point to another always results in a change in only one input variable.

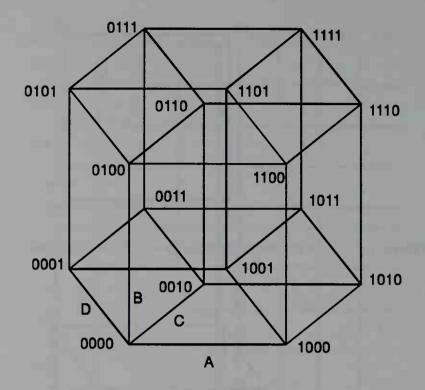

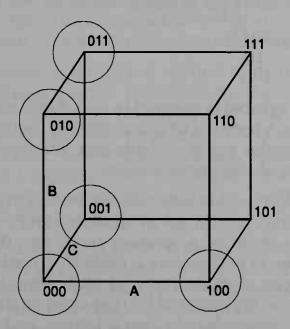

Figure 3.9 shows a four-dimensional cube (sometimes called a hyper-cube). This, of course, is a 4-cube.

Figure 3.9 Cube representation for four variables (hypercube)

# **Finding Cubes and Subcubes**

Staying with the 3-cube for the moment, let's examine some of the ways in which the cube representation can be used. The 3-cube has, as components, a number of smaller cubes. Each face of the cube, in fact, is a 2-cube. Every 3-cube, then, has six smaller *subcubes* that are identified by the input variables represented by the line segments associated with the subcube. In Figure 3.10, the indicated subcube is

Figure 3.10 Identifying subcubes on a 3-cube

defined by the 3-cube corners with the values 100, 101, 111, and 110.

Notice that the first variable in these four points remains unchanged, while at least one of the second and third variables changes from one point to the next. The second and third variables are therefore the variables that define the subcube. These variables are said to be unspecialized in relation to that subcube, while the first variable is specialized. If we specialize one of the two variables of the resulting 2-cube (or specialize two variables of the 3-cube), we end up with a 1-cube. We can even go as far as specializing all the variables of a cube, in which case we find ourselves with  $2^n$  0-cubes, where n is the number of input variables (a 0-cube simply corresponds to one point on a cube). If we map the minterms of a logic function onto a cube, we can quickly recognize subcubes of the function. Consider the following 3-variable minsum function:

!A & B & !C # !A & B & C # !A & !B & C # !A & !B & !C

Figure 3.11 shows how this function is mapped onto a 3-cube. Four of the minterms of this function form a complete 2-cube. This 2-cube is defined by specialization of the variable A, so we can immediately recognize that these four minterms can be replaced by a single product term that consists of nothing but !A. In addition, the 1-cube that is

Figure 3.11 Mapping a 3-variable function onto a cube

formed by the minterms 100 and 000 can be reduced to the simpler product term !B & !C, since A is unspecialized for that subcube. The minimized function is then

!A # !B & !C

The K-map presented earlier is simply a convenient representation of a cube and a method for quickly identifying subcubes.

## **Tabular Representation of Sum of Products**

In the K-map and cube representations, we use the values 0 and 1 to represent the complement and true values of input variables. This helps to simplify the identification and combination of cubes and subcubes within the function, but requires that the function be expressed in its minsum form.

Many logic minimization algorithms utilize another representation that doesn't require that the function be expressed in minsum form. Like the K-map representation, complement and true variables are indicated by a 0 or 1, respectively, and another symbol, the dash, is used to indicate that a variable of the function isn't used (is unspecialized) for a specific product term. To represent the four-variable function

A & !B & C & D # B & !C # A & D

in tabular form, for example, we write

1011

-10-

1--1

The dash symbol is referred to as a don't-care input condition since, for the product term in which a dash is found, we don't care what value that particular input variable has; the product term will evaluate to 1 regardless of that input's value.

As you may have already realized, this form is convenient for recognizing or obtaining such things as minterms and cubes. A minterm is indicated whenever there is a product term row that contains no dashes. A minsum form is therefore a table that contains no dashes whatsoever. The number of dashes in a product term indicates the dimensions of the subcube represented by that entry in the table: two dashes indicate a 2-cube, one dash indicates a 1-cube, and no dash indicates a 0-cube, which is, as we said, a minterm.

To convert the preceding table to minsum form, you replace each row of the table with however many rows are required to eliminate the dashes. For example, the last row becomes four rows as follows:

- (1) 1--1 10-1 11-1

- (2) 10-1 1001 1011 11-1 1101 1111

# **Prime Implicants**

In a sum of products expression, each product term is called an implicant of the logic function. If any product term evaluates to a 1, it implies that the entire function will evaluate to a 1, regardless of the value of the other product terms. Consider the following minsum expression:

!A & B & C & D # A & B & C & D # A & B & !C & D # !A & B & !C & D

Each of the four minterms in this expression is an implicant of the logic function represented by the expression since, if any of these minterms evaluates to a 1, the entire expression will also evaluate to a 1. These four minterms aren't the only implicants of the function, however.

When the expression is simplified, we find that the first two minterms can be combined into a single product term B & C & D by elimination of the variable A. Similarly, the third and fourth minterms can be combined to form the product term B & !C & D, also by elimination of the variable A. These two smaller product terms are therefore also implicants of the function, since any input condition that results in either of these product terms evaluating to 1 will result in the entire expression evaluating to 1 as well.

The implicant product terms B & C & D and B & !C & D can, of course, be simplified further by eliminating the variable C. The resulting product term B & D is what is called a *prime implicant* of this logic function. Since this logic function has only one prime implicant, that single product term represents the minimal form for the logic function.

To summarize, a prime implicant is any implicant of a logic function that is not implied by any other subfunction. A logic function may have any number of prime implicants.

## **Minimal Cover**

The set of prime implicants for a given logic function is unique, since it is determined from a unique set of minterms. It isn't always necessary, however, to use all the prime implicants for a function to obtain the minimal sum of products form. This is true because one prime implicant for a function may cover a number of minterms, and overlaps can exist; a single minterm can be covered by more than one prime implicant.

The goal of total sum of products logic minimization is to determine a minimal subset of prime implicants that will cover all the minterms of the function. This subset of prime implicants is called a *minimal cover*. The important thing to understand about prime implicants is that the fully minimized form of a logic function will consist of nothing but prime implicants, but may not require all the prime implicants for the function.

## **Essential Prime Implicant**

The search for the elusive minimal cover of prime implicants can be hastened if we first attempt to determine which prime implicants are required in a fully minimized sum-of-products representation of the function. These prime implicants are known as *essential prime implicants* and can't be eliminated from the function by any means. For example, the three-variable function

!A & !C # !A & B # A & C # A & !B

is composed entirely of prime implicants. This is not, however, the minimal sum of products form for this function. Two of the prime implicants, !A & !C and A & !B, are essential prime implicants and must be maintained. The remaining two prime implicants are not essential and can be replaced by the single prime implicant B & C, resulting in the function

!A & !C # B & C # A & !B.

# The Quine-McCluskey Procedure

The methods of logic minimization presented thus far are useful to help understand the minimization process, but are not generally applicable to large designs with more than five or six variables. In addition, these methods are difficult to implement on a computer, due to their reliance on pattern recognition.

The Quine-McCluskey procedure is a tabular method of logic minimization that can be performed manually or implemented on a computer. This method is composed of two algorithms. The first algorithm determines all the prime implicants for a given logic function, and the second selects from this set of prime implicants a subset that provides a minimal full cover for the function. The Quine-McCluskey procedure has been largely replaced by more efficient minimization methods, but it is nonetheless valuable for developing an understanding of logic minimization algorithms in general.

# **Determining Prime Implicants**

As in the K-map method, the unity theorem (A & B # !A & B = B) is used. A simplistic way to describe this process is to say that the algorithm first determines the complete set of minterms for the function and then utilizes the unity theorem repeatedly for all possible pairs of product terms to obtain all the prime implicants of the function. In this process, each pair of minterms is examined to determine if the two minterms differ by exactly one position. Pairs so identified are combined into a single product term having one fewer literal than the previous two. After all minterm pairs have been examined, the process is repeated for the resulting terms. This process is continued until we are left with the set of prime implicants. A prime implicant is identified by the fact that it can't be compared in this way with any other term.

This determination of prime implicants can be very time consuming, particularly for functions with a large number of variables. The Quine-McCluskey method uses the tabular representation described earlier to speed this process.

We'll use an example to illustrate the algorithm. Consider a four-input logic function

f(w,x,y,z)

To perform a tabular comparison, the minterms for this function are listed in order of the number of ones in the tabular assignment, as

```

WXYZ

0000

!w & !x & !y & !z

0010

!w & !x & v & !z

!w & x & !v & !z

0100

w & !x & !y & !z

1000

0101

!w & x & !v & z

w & !x & y & !z

1010

1100

w & x & !y & !z

w & !x & y & z

1011

w & x & !v & z

1101

w&x&y&z

1111

```

Figure 3.12 Minterms for a 4-input logic function

shown in Figure 3.12. This ordering assists in the identification of paired minterms.

Figure 3.13 shows the steps used in the process of searching for prime implicants. The second list is determined by combining those minterms that differ by one position, as described previously. In the second list, the dash (don't-care) replaces the removed variable. The two terms that are combined to create the entry in the second list are marked with an asterisk in the first list, indicating that they can't be prime implicants.

| LIST 1 LIST 2 LIST | _3 |

|--------------------|----|

| 0000 * 00-0 * -0-0 |    |

| 0010 * 0-00 *00    |    |

| 0100 * -000 * -10- |    |

| 1000 *             |    |

| 010 *              |    |

| 0101 * 010- *      |    |

| 1010 * -100 *      |    |

| 1100 * 10-0 *      |    |

| 1-00 *             |    |

| 1011 *             |    |

| 1101 * -101 *      |    |

| 1111 * 101-        |    |

| 110- *             |    |

|                    |    |

| 1-11               |    |

| 11-1               |    |

Figure 3.13 Finding prime implicants by tabular comparison

Having marked an entry in the first list doesn't complete the comparison process for that entry, however; each entry in the list must be compared with every other entry to eliminate all possible nonprime implicants. This means that there are  $n^2$  comparisons required for the first list alone, where n is the number of minterms in the list. In practice, the ordering of the list (by the number of ones in each product term) means that not all pairs need to be examined, speeding the comparison process.

When all the entries in the first list have been so compared, the process is repeated for the second list to create the third list. Note that, during the comparisons for the second and subsequent lists, candidate pairs must have dashes in the same position. It isn't possible, for example, to compare the terms 1-00 and -101.

When all the entries in the second list have been compared, three entries are left that are not marked. These entries are prime implicants. Attempts to compare the third list produce no combinations, so we are left with the three prime implicants from the second list plus the three in the third for a total of six prime implicants for the function. This technique for finding prime implicants has general applicability beyond the Quine-McCluskey method and is frequently used.

## **Determining a Minimal Cover**

The second step in the Quine-McCluskey method is the determination of a minimal cover for the function, using the prime implicants found as a result of the first step. This is done by first creating a covering table as shown in Figure 3.14. The covering table shows all the minterms of the function and which minterms are covered by which prime impli-

|      | 0000  | 0010 | 0100 | 0101 | 1000 | 1010 | 1011 | 1100 | 1101 | 1111 |

|------|-------|------|------|------|------|------|------|------|------|------|

| 1-1- |       |      |      |      |      | X    | X    |      |      |      |

| 1-11 |       |      |      |      |      |      | X    |      |      | X    |

| 11-1 |       |      |      |      |      |      |      |      | X    | X    |

| -0-0 | X     | X    |      |      | X    | X    |      |      |      |      |

| 00   | X     |      | X    |      | X    |      |      | X    |      |      |

| -10- | [ × 3 |      | X    | X    |      |      |      | X    | X    |      |

Figure 3.14 Covering table

|      | 1011    | 1111 |

|------|---------|------|

| 101- | X       |      |

| 1-11 | X       | X    |

| 11-1 | - 4 1-1 | X    |

Figure 3.15 Reduced covering table

cants. Obviously, it will speed the process if this covering table is constructed from the comparison information determined during the first step. The rows of the table list the prime implicants identified, while the columns represent the minterms of the function.

When the covering table has been completed, we can easily identify the essential prime implicants. These are the implicants (in this case the terms -0-0 and -10-) that are the only covers for one or more minterms. In the covering table, the essential prime implicants are entered in bold-face.

Since we know that the essential prime implicants must appear in the minimal cover, we can simplify the covering table by removing the rows corresponding to these essential prime implicants and all the columns corresponding to minterms covered by them. This simplification leaves us with the reduced covering table shown in Figure 3.15.

This reduced table shows that the prime implicant 1-11 covers both of the remaining minterms, so this prime implicant, combined with the two essential prime implicants previously identified, comprises the minimal cover for the function. The minimal cover, expressed in equation form, is then

w & y & z # !x & !z # x & !y

# 3.2 ON-SETS, OFF-SETS, AND DC-SETS

When a logic function is described, it can be expressed in one of many ways. When we describe a function using the form of Boolean equations we presented earlier, we are describing the set of input conditions that will cause the expression to evaluate true. We call this set of input conditions the *on-set*. All other input conditions will result in the expression evaluating to false. This set of implied conditions is called the *off-set*. When we describe a function by specifying only its on-set (as when using Boolean equations), we must assume that all conditions not covered in the description comprise the off-set. Similarly, if a function

Figure 3.16 Incompletely specified truth table

is described only by its off-set, then it must be assumed that all unspecified conditions form the on-set.

The truth table representation is used to describe a logic function by specifying both its on-set (indicated by ones) and off-set (indicated by zeroes). For many (perhaps most) logic designs, certain input conditions will never be encountered by the circuitry being described. Also, some input conditions may only occur at times when the output of the circuit will be unused. This information about the design can be used to advantage when minimizing the logic for that circuitry. If we know that, for certain input conditions, the output may be either true or false with no effect on the operation of the system, we can reduce the amount of circuitry required to implement the function. These input conditions are collectively referred to as the don't-care set, or *dc-set*. This is best illustrated in a truth table. Figure 3.16 shows an ABEL truth table representation of a three-variable logic function.

This truth table is only partially complete; the value of the output variable Y is missing for the input conditions, where A, B, and C are 111 or 001. This truth table is what we call an incompletely specified truth table.

The missing conditions are implied by omission, and are the don't-care conditions for Y. The truth table rows that specify a 1 for Y are conditions belonging to the on-set, while the remaining rows are the conditions

Figure 3.17 Two forms of a partially specified logic function

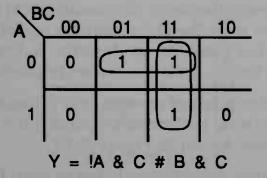

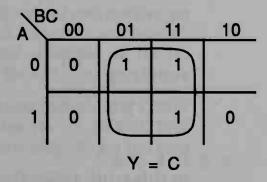

| AB | C 00 | 01 | 11 | 10 |

|----|------|----|----|----|

| 0  | 0    | 1  | 1  |    |

| 1  | 0    |    | 1  | 0  |

Figure 3.18 Indicating don't-cares on a K-map

that are members of the off-set. The two unspecified conditions form the dc-set for this function. There are four possible nonredundant implementations for this function; two are shown in Figure 3.17. As this example demonstrates, the intelligent use of don't-cares can have a dramatic affect on the size of the circuit.

Determining the minimal implementation of a function containing don't-care conditions is simply an extension of the principles outlined earlier. To represent don't-care input conditions on a K-map, we place a dash (-) symbol on the cell corresponding to that input condition, as shown in Figure 3.18.

The K-map can be processed as though the dash symbol represented either a 1 or 0, whichever results in the minimal cover. For this K-map, we can see that replacing the dash in the lower row with a 1 will result in a reduction of logic, whereas replacing it with a 0 will not.

For many purposes, it's useful to think of the don't-care value as an actual circuit condition. This is a common approach used in circuit simulators. This means that each variable now has three possible values: true, false, and don't-care. The truth table representation allows us to specify a function by supplying the on-set and off-set, with the dc-set being implied by omission from the table. When describing a function with equations, it's usually more convenient to describe the function by supplying its on-set and dc-set. (In ABEL, the dc-set equations can be specified by using the don't-care assignment operators ?= and ?:=.) When a function is described by its on-set and dc-set, the off-set is implied. Similarly, it's possible to describe a function by supplying only the off-set and dc-set, with the on-set implied.

When you design using a combination of on-sets and off-sets, on-sets and dc-sets, or off-sets and dc-sets, you must be careful not to create overlap conditions such as those shown in Figure 3.19.

In this truth table, the same input condition is listed in both the on-set and off-set for Y. This is easy to detect in a truth table (or K-map), but is not so easy to detect if on-sets and off-sets are being expressed in

Figure 3.19 Overlapping truth table conditions

some other form (notably Boolean equations or state transitions). This is a common area of confusion for users of computer-based logic minimization tools. (The ABEL compiler will, in most cases, detect overlaps such as this and report an error.)

## 3.3 MULTIPLE-OUTPUT MINIMIZATION

When targeting a design to a simple PLD, the preceding techniques are adequate, since there is no sharing of logic from one device output to another. In PLA-type devices, however, there is opportunity for improvement. The total amount of circuitry required to implement a multiple-output function can be reduced if all outputs of the function are evaluated together.

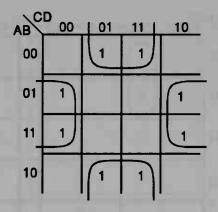

Figure 3.20 shows two three-variable functions expressed as K-maps. Each function has two prime implicants as shown. The K-maps, when overlaid, show that one prime implicant is common to both functions. Considered together, then, it is possible to implement both of these functions using a total of three product terms.

The prime implicant shared by the two functions is called a multiple-

Figure 3.20 Two functions with a shared prime implicant

Figure 3.21 Two independent functions