# **SEMICONDUCTORS**

3501 ED BLUESTEIN BLVD., AUSTIN, TEXAS 78721

### **Advance Information**

# MC68451

# MEMORY MANAGEMENT UNIT

**APRIL, 1983**

### **TABLE OF CONTENTS**

| Paragraph<br>Number | Title                                  | Page<br>Number         |

|---------------------|----------------------------------------|------------------------|

|                     | Section 1                              |                        |

|                     | Introduction                           |                        |

| 1.1                 | Memory Segments                        | 1-2                    |

| 1.2                 | Function Codes and Address Spaces      | 1-2                    |

| 1.3                 | Address Space Number                   | 1-3                    |

| 1.4                 | Descriptors                            | 1-4                    |

| 1.5                 | Translation                            | 1-4                    |

|                     | Section 2                              |                        |

|                     | Signal Description                     |                        |

| 2.1                 | VCC and GND                            | 2-1                    |

| 2.2                 | Clock                                  | 2-2                    |

| 2.3                 | Chip Select (CS)                       | 2-2                    |

| 2.4                 | Register Selects (RS1-RS5)             | 2-2                    |

| 2.5                 | Read/Write (R/W)                       | 2-2                    |

| 2.6                 | RESET                                  | 2-2                    |

| 2.7                 | Data Transfer Acknowledge (DTACK)      | 2-2                    |

| 2.8                 | Upper and Lower Data Strobe (UDS, LDS) | 2-2                    |

| 2.9                 | Address Strobe (AS)                    | 2-3<br>2-3             |

| 2.10<br>2.11        | Physical Address and Data (PAD0-PAD15) | 2-3<br>2-3             |

| 2.11                | Enable Data (ED)                       | 2-3<br>2-3             |

| 2.12                | Hold Address (HAD)                     | 2-3<br>2-3             |

| 2.13<br>2.14        | MODE                                   | 2-3<br>2-3             |

| 2.14                | Interrupt Acknowledge (IACK)           | 2-3<br>2-4             |

| 2.16                | FAULT                                  | 2-4<br>2-4             |

| 2.10                | Function Codes (FC0-FC3)               | 2- <del>4</del><br>2-4 |

| 2.17                | Address Bus (A8-A23)                   | 2-4                    |

| 2.19                | Global Operation (GO)                  | 2- <del>4</del><br>2-4 |

| 2.10                | ANY                                    | 2-4                    |

| 2.20                | ALL                                    | 2 <del>-4</del><br>2-5 |

| 2.21                | Mapped Address Strobe (MAS)            | 2-5<br>2-5             |

| 2.23                | Write Inhibit (WIN)                    | 2-5<br>2-5             |

|                     |                                        |                        |

|                     | Section 3 Register Description         |                        |

| 3.1                 | Descriptors                            | 3-2                    |

| 3.1.1               | Logical Base Address (LBA)             | 3-2                    |

| 3.1.2               | Logical Address Mask (LAM)             | 3-2                    |

| 3.1.3               | Physical Base Address (PBA)            |                        |

# TABLE OF CONTENTS (Continued)

| Paragraph<br>Number | Title                              | Page<br>Number |

|---------------------|------------------------------------|----------------|

| 3.1.4               | Address Space Number (ASN)         | 3-3            |

| 3.1.5               | Address Space Mask (ASM)           | 3-3            |

| 3.1.6               | Segment Status Register (SSR)      | 3-3            |

| 3.2                 | System Registers                   | 3-4            |

| 3.2.1               | Address Space Table (AST)          | 3-4            |

| 3.2.2               | Accumulator (AC0-AC8)              | 3-5            |

| 3.2.3               | Global Status Register (GSR)       | 3-6            |

| 3.2.4               | Local Status Register (LSR)        | 3-6            |

| 3.2.5               | Descriptor Pointer (DP)            | 3-7            |

| 3.2.6               | Result Descriptor Pointer (RDP)    | 3-8            |

| 3.2.7               | Interrupt Descriptor Pointer (IDP) | 3-8            |

| 3.2.8               | Interrupt Vector Register (IVR)    | 3-9            |

|                     | Section 4                          |                |

| 4.4                 | MMU Functional Description         |                |

| 4.1                 | Single-MMU Systems                 | 4-1            |

| 4.2                 | Multiple-MMU Systems               | 4-1            |

| 4.3                 | MMU Timing                         | 4-5            |

| 4.4                 | MMU Flow Diagram                   | 4-5            |

| 4.5                 | MMU Functional States              | 4-5            |

| 4.5.1               | The Reset State                    | 4-10           |

| 4.5.2               | The Idle State                     | 4-11           |

| 4.5.3               | Normal Address Translation         | 4-11           |

| 4.5.3.1             | Matching                           | 4-11           |

| 4.5.3.2             | Successful Translation             | 4-11           |

| 4.5.3.3             | Write Violation                    | 4-12           |

| 4.5.3.4             | No Address Match                   | 4-12           |

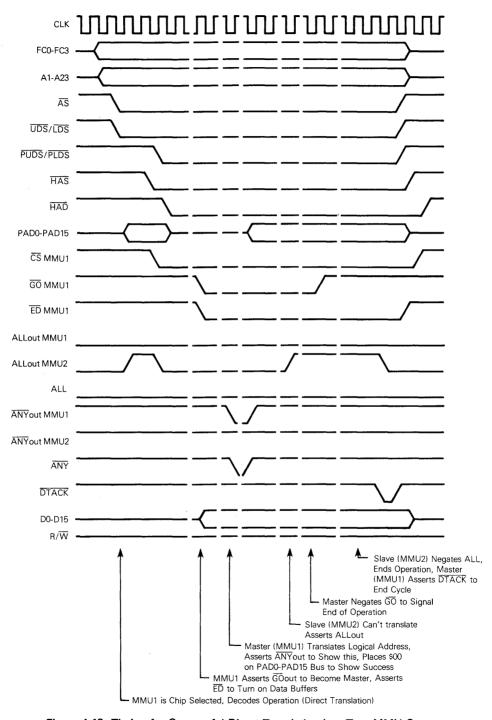

| 4.5.3.5             | External Translation               | 4-12           |

| 4.5.3.6             | External Write Violation           | 4-13           |

| 4.5.3.7             | Undefined Segment Access           | 4-14           |

| 4.6                 | MMU Operations                     | 4-16           |

| 4.6.1               | Operations Address Map             | 4-17           |

| 4.6.2               | Local Operations                   | 4-17           |

| 4.6.2.1             | Interrupt Acknowledge              | 4-18           |

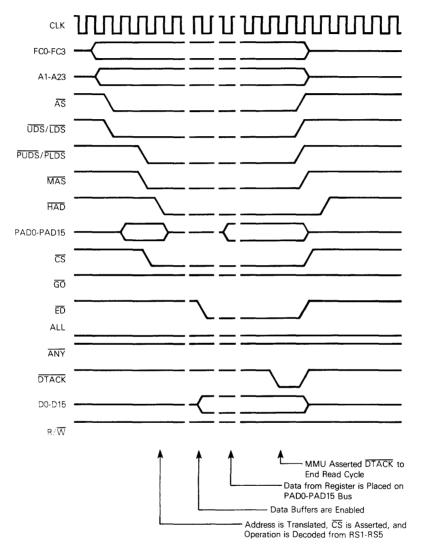

| 4.6.2.2             | Read System Register               | 4-18           |

| 4.6.2.3             | Transfer Descriptor                | 4-18           |

| 4.6.2.4             | Write Segment Status Register      | 4-18           |

| 4.6.2.5             | Null Operation                     | 4-18           |

| 4.6.3               | Global Operations                  | 4-18           |

| 4.6.3.1             | Write System Register              | 4-18           |

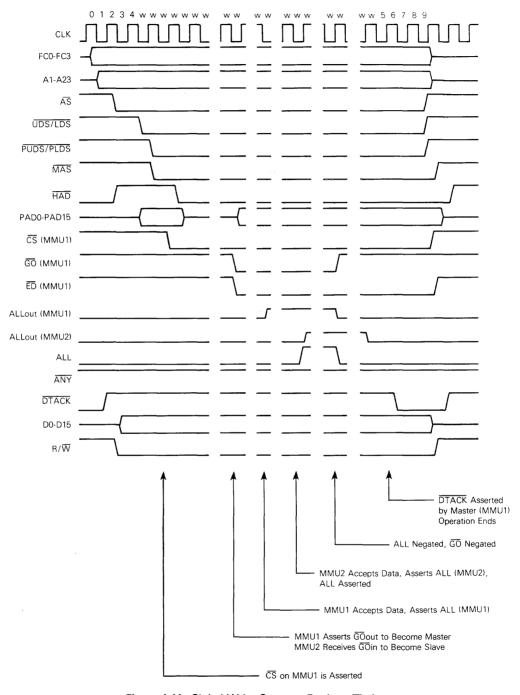

| 4.6.3.2             | Load Descriptor Operation          | 4-23           |

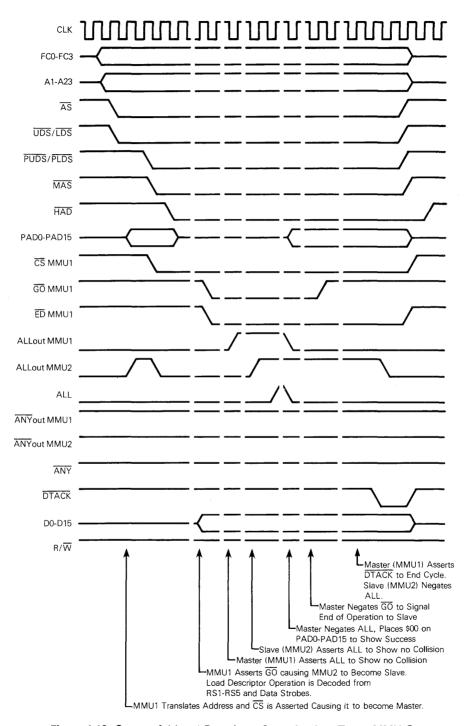

| 4.6.3.3             | Direct Translation                 | 4-23           |

| 4.7                 | Operation Length Table             | 4-24           |

# TABLE OF CONTENTS (Concluded)

| Paragraph<br>Number | Title                                 | Page<br>Number |

|---------------------|---------------------------------------|----------------|

|                     | Section 5                             |                |

|                     | Hardware Considerations               |                |

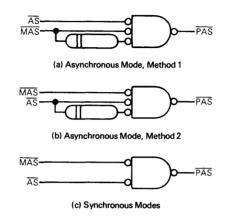

| 5.1                 | MAS Timing Modes and Physical Address | 5-1            |

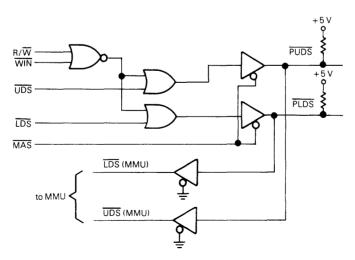

| 5.2                 | Physical Data Strobes                 | 5-2            |

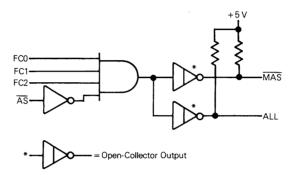

| 5.3                 | Interrupts                            | 5-3            |

|                     | Section 6                             |                |

|                     | Software Considerations               |                |

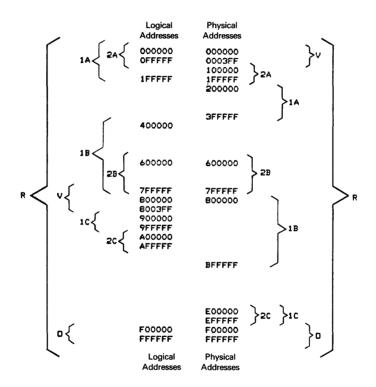

| 6.1                 | Segment Mapping Example               | 6-1            |

| 6.2                 | Segmentation                          | 6-4            |

| 6.3                 | Virtual Memory Support                | 6-4            |

| 6.4                 | Initialization Software               | 6-4            |

| 6.5                 | Context Switching                     | 6-5            |

|                     | Section 7                             |                |

|                     | Electrical Specifications             |                |

| 7.1                 | Maximum Ratings                       | 7-1            |

| 7.2                 | Thermal Characteristics               | 7-1            |

| 7.3                 | Power Considerations                  | 7-1            |

| 7.4                 | AC Electrical Specifications          | 7-2            |

| 7.5                 | Electrical Characteristics            | 7-4            |

|                     | Section 8                             |                |

|                     | Mechanical Data                       |                |

| 8.1                 | Ordering Information                  | 8-1            |

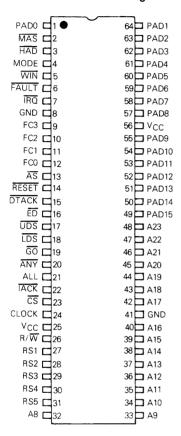

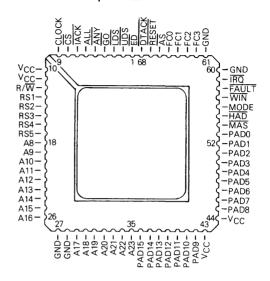

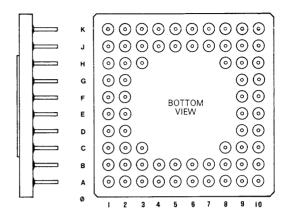

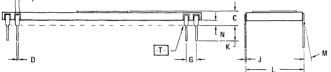

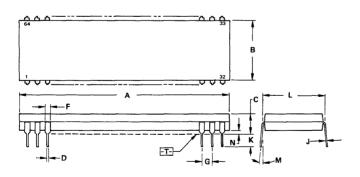

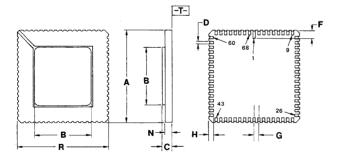

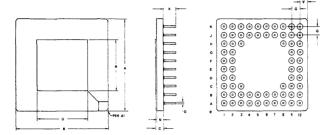

| 8.2                 | Pin Assignments                       | 8-2            |

| 8.3                 | Package Dimensions                    | 8-3            |

### LIST OF ILLUSTRATIONS

| Figure<br>Number | Title                                                        | Page<br>Number |

|------------------|--------------------------------------------------------------|----------------|

| 1-1<br>1-2       | Simplified Block Diagram of Single-MMU System                | 1-2<br>1-3     |

| 1-3              | Memory Map of Typical Task Address Space                     | 1-3            |

| 1-4              | Schematic Diagram of Descriptor Mapping                      | 1-4            |

| 1-5              | Functional Block Diagram                                     | 1-5            |

| 3-1              | Programmer's Model                                           | 3-1            |

| 3-2              | Schematic Logic of Address Matching                          | 3-2            |

| 3-3              | Schematic Logic of Physical Address Generation               | 3-3            |

| 3-4              | Address Space Table Organization                             | 3-5            |

| 4-1              | Single-MMU System with MC68000 or MC68010                    | 4-2            |

| 4-2              | Using the MC68008 with the MMU                               | 4-3            |

| 4-3              | Sample Circuit Diagram of a Two-MMU System with the MC68010  | 4-4            |

| 4-4              | MMU Flow Diagram                                             | 4-6            |

| 4-5              | Reset Flow Diagram                                           | 4-10           |

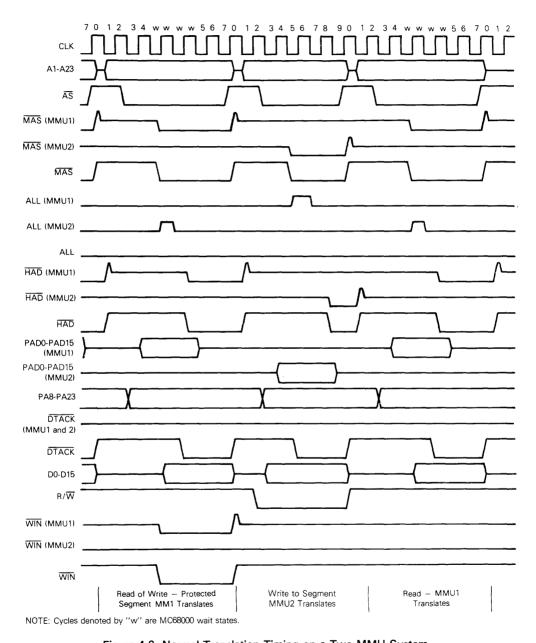

| 4-6              | Normal Translation Timing in a Two-MMU System                | 4-13           |

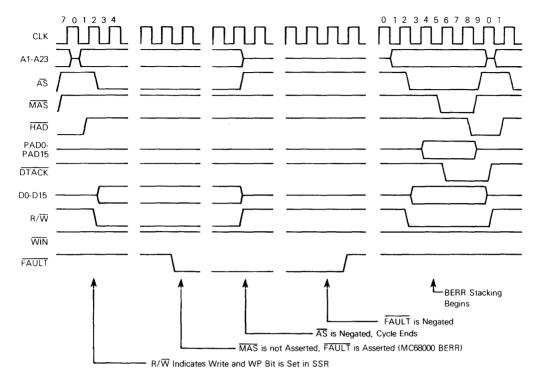

| 4-7              | Write Violation Timing                                       | 4-14           |

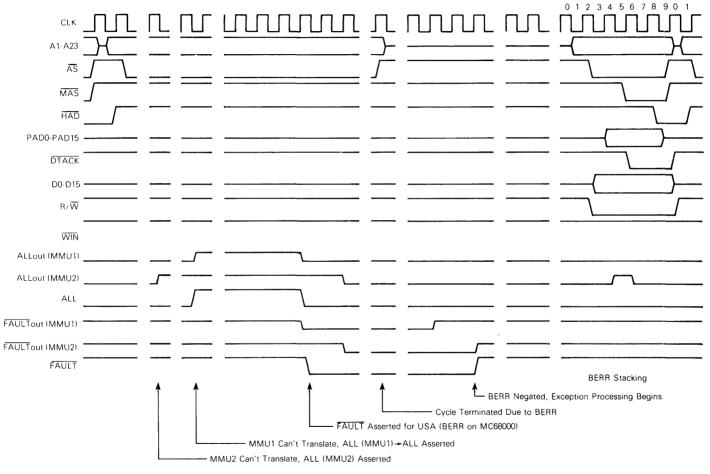

| 4-8<br>4-9       | Undefined Segment Access Timing                              | 4-15<br>4-19   |

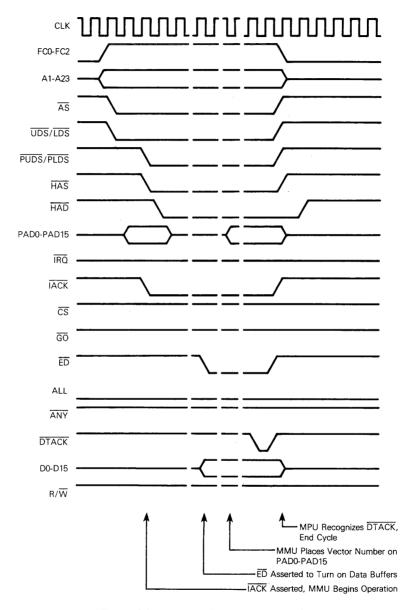

| 4-9<br>4-10      | Interrupt Acknowledge Timing                                 | 4-19<br>4-20   |

| 4-10<br>4-11     | Read System Register Timing                                  | 4-20<br>4-21   |

| 4-11<br>4-12     | Successful Load Descriptor Operation in a Two-MMU System     | 4-21<br>4-22   |

| 4-13             | Timing for Successful Direct Translation in a Two-MMU System | 4-25           |

| 5-1              | Physical Address Strobe Generation                           | 5-2            |

| 5-2              | Generation of Physical Read/Write and Physical Data Strobes  | 5-2            |

| 5-3              | Circuit to Inhibit Translation during IACK                   | 5-3            |

| 6-1              | Address Map Example                                          | 6-2            |

| 6-2              | Translation Example                                          | 6-3            |

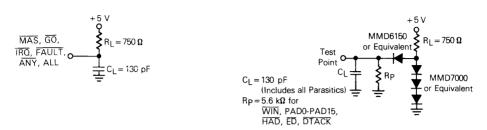

| 7-1              | Test Loads                                                   |                |

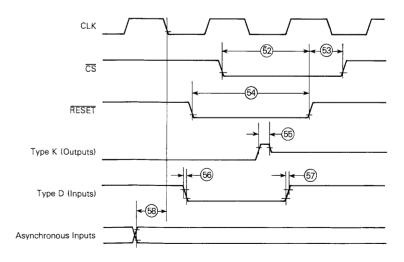

| 7-2              | Normal Translation Timing                                    |                |

| 7-3              | Operations Timing                                            |                |

| 7-4              | Miscellaneous Signal Timing                                  | Foldout 2      |

### LIST OF TABLES

| Table<br>Number | Title                                  | Page<br>Number |

|-----------------|----------------------------------------|----------------|

| 3-1             | Accumulator Assignments for Operations | 3-5            |

| 4-1             | Length of Operations                   | 4-9            |

| 4-2             | Summary of MMU Functions               | 4-16           |

| 4-3             | Register/Operations Address Map        | 4-17           |

# SECTION 1 INTRODUCTION

The MC68451 memory management unit (MMU) provides address translation and protection for the 16 megabyte addressing range of the MC68000 MPU. Each bus master (or processor) in the M68000 Family provides a function code and an address during each bus cycle. The function code specifies an address space and the address specifies a location within that address space. The function codes distinguish between user and supervisor spaces and, within these, between data and program spaces. This separation of address spaces provides the basis for memory management and protection by the operating system. Provision is also made for other bus masters, such as the MC68450 DMAC, to have separate address spaces for logical DMA. A multitasking operating system is simplified and reliability is enhanced through the use of the MMU.

#### Features of the MC68451 include:

- MC68451F Faster Translation Times

- Compatible with MC68000 and MC68008

- Provides Virtual Memory Support for the MC68010

- Provides Efficient Memory Allocation

- Separates Address Spaces of System and User Resources

- Provides Write Protection

- Supports Paging and Segmentation

- 32 Segments of Variable Size with Each MMU

- Multiple MMU Capability to Expand to Any Number of Segments

- Allows Inter-Task Communication through Shared Segments

- Quick Context Switching to Cut Operating System Overhead

- Simplifies Programming Model of Address Space

- Increases System Reliability

- DMA Compatible

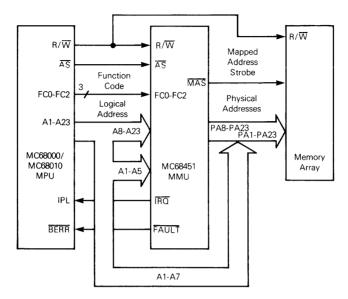

The MC68451 memory management unit (MMU) is the basic element of a memory management mechanism (MMM) in an M68000 Family system. The operating system is responsible for insuring the proper execution of user tasks in the system environment and memory management is basic to this responsibility. The MMM provides the operating system with the capability to allocate, control, and protect the system memory. A block diagram of a single-MMU system is shown in Figure 1-1.

An MMM, implemented with one or more MC68451 MMUs, can provide address translation, separation, and write protection for the system memory. The MMM can be programmed to cause an interrupt when a chosen section of memory is accessed and can directly translate a logical address into a physical address making it available to the MPU for use by the operating system. Using these features, the MMM can provide separation and security for user programs and allow the operating system to manage the memory in an efficient fashion for multitasking.

Figure 1-1. Simplified Block Diagram of Single-MMU System

#### 1.1 MEMORY SEGMENTS

The MMM partitions the logical address space into contiguous pieces called segments. Each segment is a section of the logical address space of a task which is mapped via the MMM into the physical address space. Each task may have any number of segments. Segments may be defined as user or supervisor, data-only or program-only, or program and data. They may be accessed by only one task or shared between two or more tasks. In addition, any segment can be write protected to insure system integrity. A fault (MC68000 bus error) is generated by the MMM if an undefined segment is accessed.

#### 1.2 FUNCTION CODES AND ADDRESS SPACES

Each bus master in the M68000 Family (including the MC68440 DMA controllers) provides a function code during each bus cycle to indicate the address space to be used for that cycle. The address bus then specifies a location within this address space for the operation taking place during that bus cycle.

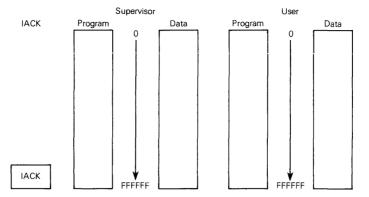

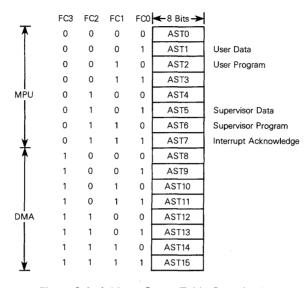

The function codes appear on the FC0-FC2 lines of the MC68000 and divide the memory references into two logical address spaces — the supervisor and the user spaces. Each of these is further divided into program and data spaces. A separate address space is also provided for internal CPU-related activities such as interrupt acknowledge, giving a total of five defined function codes. The address space of the MC68000 is shown in Figure 1-2.

In addition to the 3-bit function code provided by the MC68000, the MC68451 MMU also allows a fourth bit (FC3) which provides for the possibility of another bus master in the system. In this case, FC3 would be a function of bus grant acknowledge (BGACK) of the MC68000 to enable a second

Figure 1-2. Address Space of MC68000

set of eight function codes. This raises the total number of possible function codes to sixteen. If there is only one bus master (the MPU), the FC3 pin on the MMU should be tied low and only eight address spaces can then be used.

#### 1.3 ADDRESS SPACE NUMBER

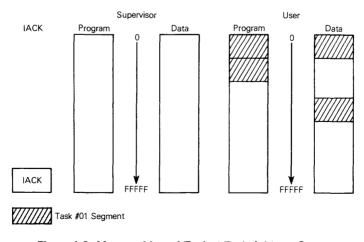

Each task in a system has an address space which is comprised of all the segments defined for that task. This address space is assigned a number by programming all the address space number (ASN) fields in its descriptors with the same value. This value can be considered a task number. The currently active task's number is kept in the appropriate entry(s) in the address space table (AST).

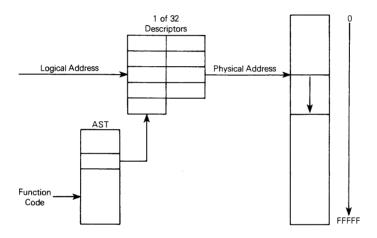

The AST is a set of MMU registers which defines which task's segments are to be used in address translation for each cycle type (supervisor program, supervisor data, etc). The AST contains an 8-bit entry for each possible function code. Each entry is assigned an ASN (task number) and this is used to select which descriptors may be used for translation. The logical address is then translated by one of these to produce the physical address. Figure 1-3 is a typical memory map of a task's address space.

Figure 1-3. Memory Map of Typical Task Address Space

#### 1.4 DESCRIPTORS

Address translation is done using descriptors. A descriptor is a set of six registers (nine bytes) which describe a memory segment and how that segment is to be mapped to the physical addresses. Each descriptor contains base addresses for the logical and physical spaces of each segment. These base addresses are then masked with the logical address masks. The size of the segment is then defined by "don't cares" in the masks. This method allows segment sizes from a minimum of 256 bytes to a maximum of 16 megabytes in binary increments (i.e., powers of two). This also forces both logical and physical addresses of segment boundaries to lie on a segment size boundary. That is, a segment can only start on an address which is a multiple of 2k. The segments can be defined in such a way to allow them to be logically or physically shared between tasks. Descriptor mapping is shown schematically in Figure 1-4.

Figure 1-4. Schematic Diagram of Descriptor Mapping

#### 1.5 TRANSLATION

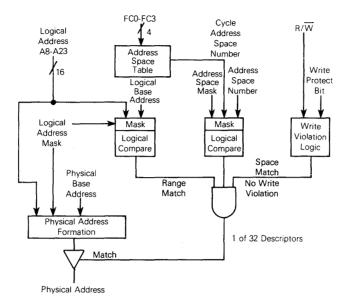

During normal translation, the MMU translates the logical address provided by the MC68000 to produce a physical address which is then presented to the memory array. This is accomplished by matching the logical address with the information in the descriptors and then mapping it into the physical address space. A block diagram of the MC68451 MMU is shown in Figure 1-5.

Refer to Figure 1-1 for the following. The logical address is composed of address lines A1-A23. The upper 16 bits of this address (A8-A23) are translated by the MMU and mapped into a physical address (PA8-PA23). The lower seven bits of the logical address (A1-A7) bypass the MMU and become the low-order physical address bits (PA1-PA7). In addition, the data strobes (UDS and LDS) remain unmapped to become the physical data strobes for a total of eight unmapped address lines.

Figure 1-5. Functional Block Diagram

### SECTION 2 SIGNAL DESCRIPTION

This section contains a brief description of the input and output signals.

#### NOTE

Throughout this document, active low signals are denoted by a superscript bar. This does not imply logical negation. To avoid confusion, a signal in its true state is said to be asserted whether that signal is active high or low. It is said to be negated when it is in its functionally inactive state. A signal which can be placed in the high-impedance state is said to be three-stated. A signal line which is first negated and then placed in the high-impedance state is said to be rescinded.

Some MMU signal lines are classed as input/output meaning that the bus buffers can be directed inward to input information into the MMU or outward to drive the bus. These signals must be either inputs or outputs at any given time, they may not be both. An example is the PAD port.

Still other types of signals can logically be both inputs or outputs at the same time. The internal signal controller may assert or negate a signal and read it at the same time. To distinguish between them, the suffix "in" will be used to denote the input signal and the suffix "out" will be used for the output signal.

Six pins on the MMU have this property  $-\overline{\text{IRQ}}$ ,  $\overline{\text{FAULT}}$ ,  $\overline{\text{MAS}}$ ,  $\overline{\text{GO}}$ ,  $\overline{\text{ANY}}$ , and ALL. In a multiple-MMU system, they would be wired in parallel to provide a single-signal level for the entire system. Of these, three pins  $-\overline{\text{IRQ}}$ ,  $\overline{\text{FAULT}}$ , and  $\overline{\text{ANY}}$  - are active low, wire-OR type signals. As such, asserting any one of the parallel pins will drive the line low (true). If any of these signals are asserted on any MMU in the system, they will be detected as asserted on the corresponding "in" pin of all MMUs in the system.

The ALL pin is an active-high open-drain gate and, as such, all pins are wire-ANDed and must be pulled high in order for the input to be high. Therefore, even if ALLout is asserted by an MMU, ALLin will not be detected true by any MMU unless all of the corresponding pins on all MMUs in the system are asserted.

The  $\overline{\text{GO}}$  and  $\overline{\text{MAS}}$  pins are not open drain but they can be put in the high-impedance state. They should each be wired in parallel on all MMUs in the system since only one MMU at any given time will assert these signals. A pullup resistor is required to hold the signal inactive when the pin is in the high-impedance state.

#### 2.1 VCC AND GND

These pins supply power to the MMU. The two VCC pins are  $\pm 5\%$  and the two GND pins are ground.

#### 2.2 CLOCK

This TTL input signal must be the MC68000 system clock and must not be gated off at any time.

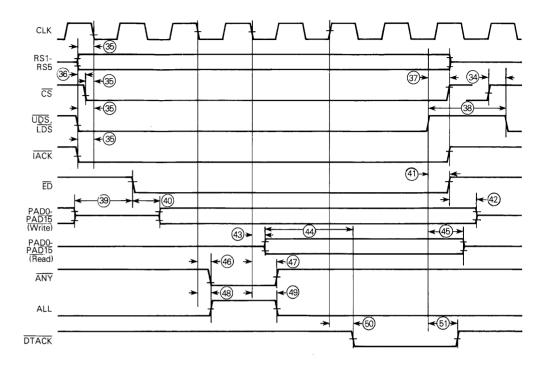

#### 2.3 CHIP SELECT (CS)

$\overline{\text{CS}}$  is an input used to activate the MMU for accesses to the registers and other MMU operations. The assertion of  $\overline{\text{CS}}$ , in conjunction with the address of a global operation on pins RS1-RS5, selects the MMU to be a master for that operation.  $\overline{\text{CS}}$  should be decoded from the physical address bus to protect the MMU registers from unauthorized access. See **4.6 MMU OPERATIONS.**

#### 2.4 REGISTER SELECTS (RS1-RS5)

These five input pins should be the lower five bits of the physical address bus. When  $\overline{CS}$  is asserted, these pins select the operation to be performed and the register involved (if any). See Table 4-3 for the operations address map.

#### 2.5 READ/WRITE (R/W)

The  $R/\overline{W}$  input signal controls the direction of the data bus during an MMU operation. It is also used to compare against the matched descriptor to determine if a write violation has occurred during translation.

#### 2.6 RESET

Asserting the RESET input will reset the MMU regardless of what state it is in. The RESET pin must be held low for at least 16 clock cycles to reset the MMU. During power up, the RESET pin must be held low for at least 100 milliseconds after VCC is established and the clock signal is present. See 4.5.1 The Reset State.

#### 2.7 DATA TRANSFER ACKNOWLEDGE (DTACK)

The MMU uses this rescindable output to signal the completion of the operation phase of a bus cycle to the processor. If the bus cycle is a processor read, the MMU asserts  $\overline{\text{DTACK}}$  to indicate that the information on the data bus is valid. If the bus cycle is a processor write to the MMU,  $\overline{\text{DTACK}}$  is used to acknowledge acceptance of the data by the MMU.  $\overline{\text{DTACK}}$  may be asserted only by an MMU that has  $\overline{\text{CS}}$  or  $\overline{\text{IACK}}$  asserted.

#### 2.8 UPPER AND LOWER DATA STROBES (UDS, LDS)

The UDS and LDS inputs are used during MMU operation (processor access of MMU registers) to indicate which byte of the data bus is to be used. The assertion of the upper data strobe indicates that the operation is to be performed at an even address using the upper byte of the data bus. The assertion of lower data strobe indicates that the operation is to be performed at an odd address using the lower byte of the data bus. During a processor write operation, the data strobes indicate to the MMU that valid data is on the data bus.

#### 2.9 ADDRESS STROBE (AS)

This input signal indicates to the MMU that a bus cycle is in progress, and that there is a valid address on the logical address bus. The assertion of  $\overline{AS}$  initiates the normal translation phase of the bus cycle.

#### 2.10 PHYSICAL ADDRESS AND DATA (PAD0-PAD15)

During MMU operations, these 16 multiplexed input/output pins function as the data bus used to transfer data to and from the MMU. During normal translation, the physical address PA8-PA23 is gated out on this bus. External octal data transceivers are used to isolate the system data bus from the physical address bus. The MMU provides the enable data (ED) signal to control these transceivers. See 2.11 ENABLE DATA for more detail.

#### 2.11 ENABLE DATA (ED)

The enable data signal is a three-state output signal used to control the external bus transceivers on the PAD0-PAD15 bus. When  $\overline{\text{ED}}$  is asserted, the transceivers should be enabled (i.e., they should drive the bus). When  $\overline{\text{ED}}$  is negated, the transceivers should be in the high-impedance state.  $R/\overline{W}$  is used to control the direction of the transceivers. Only the MMU with  $\overline{\text{CS}}$  or  $\overline{\text{IACK}}$  asserted will assert  $\overline{\text{ED}}$ .

#### NOTE

A pair of SN74LS245 type data transceivers may be used. ED will drive the output enable pin with no additional logic. See the circuit diagram in Section 4 (Figure 4-1).

#### 2.12 HOLD ADDRESS (HAD)

HAD is a rescindable output used to control an external latch on the physical address bus. After normal translation, HAD is asserted to hold the physical address stable. The latch should be of the transparent type such as an SN74LS373. HAD can directly interface with the enable pin of this type of latch. To provide address hold time, HAD is rescinded after MAS is rescinded.

#### 2.13 MODE

MODE is a three-level input used to program the mode of operation of the  $\overline{MAS}$  signal. There are three modes of operation: A, S1, and S2.

Mode A is selected by leaving the MODE pin unconnected. Mode S1 is selected by tying the MODE pin to VCC and mode S2 is selected by tying the MODE pin to ground. For description of the different modes, see **SECTION 5 HARDWARE CONSIDERATIONS**.

#### 2.14 INTERRUPT REQUEST (IRQ)

IRQ is an open-drain input/output signal. IRQout is used to request an interrupt of the MPU. IRQout is asserted if a descriptor in which the I (interrupt) bit is set, is matched in normal translation, and the interrupt enable (IE) bit in the global status register (GSR) is set. Clearing all IP (interrupt pending) bits in all segment status registers or clearing IE in the GSR will cause IRQ to be negated. If IRQin and IACK, and UDS and/or LDS, are asserted, the MMU will perform an interrupt

acknowledge operation. See **4.6 MMU OPERATIONS.** The  $\overline{\text{IRQ}}$  lines of all MMUs should be wire-ORed together and tied to V<sub>CC</sub> through a pullup resistor. They should be isolated from the  $\overline{\text{IRQ}}$  lines of other devices to prevent an MMU from detecting an erroneous interrupt.

### 2.15 INTERRUPT ACKNOWLEDGE (IACK)

An MMU will begin the interrupt acknowledge operation if  $\overline{IRQ}$  in and  $\overline{IACK}$  are both asserted. The interrupt vector supplied by the interrupt vector register (IVR) is placed on the data bus for the MPU. Only one MMU should have its  $\overline{IACK}$  pin tied to the  $\overline{IACK}$  circuitry from the processor; all other MMUs should have this pin tied high (inactive).

#### 2.16 FAULT

FAULT is an open-drain input/output signal. During normal translation, if an MMU detects a write violation or an undefined segment access, it asserts the FAULT line for five clock cycles or until AS becomes negated, whichever is longer. If an MMU detects FAULT in asserted, it updates its global and local status registers to reflect this. The FAULT lines of all MMUs in the system should be wire-ORed and tied to VCC through a pullup resistor. The FAULT signals can be connected directly to the MC68000 BERR pin but they should be isolated from any other bus error signals in the system to prevent the MMUs from detecting an erroneous FAULT.

#### 2.17 FUNCTION CODES (FC0-FC3)

The function code inputs specify the type of bus cycle being executed by the current bus master. The function code indicates which address space is to be used for that cycle and is used to index into the address space table for the cycle address space number used in descriptor matching. See 1.2 FUNCTION CODES AND ADDRESS SPACES.

#### 2.18 ADDRESS BUS (A8-A23)

These inputs are the upper 16 bits of the MPU address bus. They form the logical address which the MMU translates into 16 physical-address bits. The lower seven address lines (A1-A7) bypass the MMU.

#### 2.19 GLOBAL OPERATION (GO)

$\overline{\text{GO}}$  is a rescindable input/output inter-MMU signal used in multiple-MMU systems to indicate or detect global operations. If  $\overline{\text{CS}}$  is asserted and the operation to be performed is global, the MMU is selected as the master MMU for that operation.  $\overline{\text{GO}}$ out is then asserted by the master MMU to signal other MMUs that they are slaves in a global operation. Thus, if  $\overline{\text{GO}}$ in is asserted while  $\overline{\text{CS}}$  is negated, the MMU is selected as a slave for that operation. For a detailed description, see **4.6 MMU OPERATIONS**.

#### 2.20 ANY

The  $\overline{\text{ANY}}$  signal is an open-drain input/output inter-MMU handshake signal for multiple-MMU systems. A slave MMU asserts  $\overline{\text{ANY}}$  out during a global operation if it has a local event to report which is significant if it occurs in one, but not necessarily all, MMUs. The  $\overline{\text{ANY}}$  pins are wire-ORed and require a pullup resistor to VCC.

#### 2.21 ALL

The ALL pin is an open-drain input/output similar to  $\overline{\text{ANY}}$  except that it reports events that are significant only when they occur in all MMUs. The ALL pins are wire-ANDed together and require a pullup resistor to VCC.

#### 2.22 MAPPED ADDRESS STROBE (MAS)

MAS is a rescindable input/output signal. MASout is asserted by an MMU if an address match occurs during normal translation. This indicates that a valid physical address is present at the PADO-PAD15 outputs. MAS in is used by an MMU to detect a successful translation by another MMU. MAS can be programmed to operate in an asynchronous or synchronous mode by the MODE pin.

#### 2.23 WRITE INHIBIT (WIN)

WIN is a rescindable output provided to protect write-protected segments during read-modify-write bus cycles. Normally, write-protected segments are protected by the assertion of FAULT and the withholding of MAS upon detection of an attempted write to that segment. However, during read-modify-write bus cycles, AS remains asserted, making it difficult to prevent the write portion of the instruction from writing to the protected segment. To provide write protection during these instructions, WIN should be included in the decoding of the physical data strobes. See 5.2 PHYSICAL DATA STROBES. WIN is asserted with MAS each time a write-protected segment is accessed, whether the access is a read or a write.

#### NOTE

In multiple-MMU systems,  $\overline{\text{MAS}}$ ,  $\overline{\text{HAD}}$ ,  $\overline{\text{WIN}}$ ,  $\overline{\text{FAULT}}$ ,  $\overline{\text{DTACK}}$ ,  $\overline{\text{ED}}$ , and  $\overline{\text{GO}}$  should be connected in parallel to their respective pins on all MMUs. Each should be tied to VCC through a pullup resistor to insure that the signal is negated while the pin is in the high-impedance state.

# SECTION 3 REGISTER DESCRIPTION

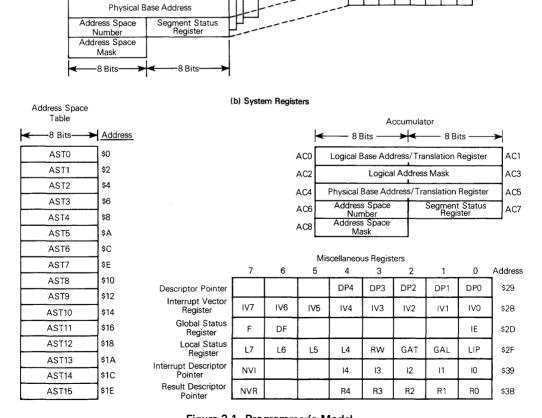

Figure 3-1 shows a programmer's model of the MMU. The MMU registers consist of two groups: the descriptors and the system registers. Each of the 32 descriptors is nine bytes long and defines one memory segment. See **3.1 DESCRIPTORS**.

(a) Descriptors (32)

Segment Status Register

ΙP

M WP E

Logical Base Address

Logical Address Mask

Figure 3-1. Programmer's Model

In the following discussion, a segment access is defined as a successful match occurring on a segment during normal translation.

The system registers contain both information local to the MMU and information global to the MMM. Each bit in the system registers and the segment status registers, except the address space table, is one of four types:

Control Control bits can be set or cleared by the MPU to select MMU op-

tions. These are read/write bits.

Status Alterable SA bits are set or cleared by the MMU to indicate status information.

These are also read/write bits.

Status Unalterable SU bits are set or cleared by the MMU to reflect status information.

These bits cannot be written by the MPU.

Reserved bits are reserved for future expansion. They cannot be writ-

ten and are zero when read.

The system registers are all directly addressable from the physical-address space. Accessing registers causes certain operations to be performed. See **4.6.1 Operations Address Map** for the locations of system registers. The descriptors are not directly addressable, but are accessed using the descriptor pointer and the accumulator.

#### 3.1 DESCRIPTORS

Each MMU contains 32 descriptors (0-31), each of which can define one memory segment. A descriptor is loaded by the MPU using the accumulator and descriptor pointer with a load descriptor operation. The segment status register (SSR) can be written to by the MPU indirectly using the descriptor pointer. Each descriptor consists of the following registers.

#### 3.1.1 Logical Base Address (LBA)

The LBA is a 16-bit register which, together with the logical address mask (LAM), defines the logical addressing range of a segment. This is typically the first address in the segment, although it can be any address within the range defined by the LAM.

#### 3.1.2 Logical Address Mask (LAM)

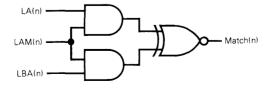

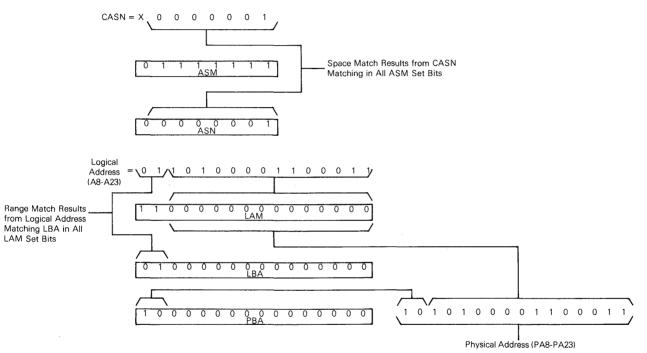

The LAM is a 16-bit mask which defines the bit positions in the LBA which are to be used for range matching. Ones, in the mask, mark significant bit positions while zeroes indicate "don't care" positions. A range match occurs if, in each bit position in the LAM which is set to one, the LBA matches the incoming logical address. The matching function is depicted schematically in Figure 3-2.

Figure 3-2. Schematic Logic of Address Matching

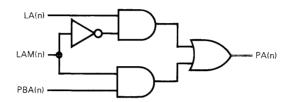

#### 3.1.3 Physical Base Address (PBA)

The PBA is a 16-bit address which, with the LAM and the incoming logical address, is used to form the physical address. The logical address is passed through to the physical address in those bit positions in the LAM which contain zeroes (the "don't cares") and the PBA is gated out in those positions which contain ones. A schematic representation of the physical address generation mechanism is shown in Figure 3-3.

Figure 3-3. Schematic Logic of Physical Address Generation

#### 3.1.4 Address Space Number (ASN)

The ASN is an 8-bit number which, together with the address space mask, is used in detecting a match with the cycle address space number.

#### 3.1.5 Address Space Mask (ASM)

The ASM is an 8-bit mask which defines the significant bit positions in the ASN which are to be used in descriptor matching. As in the LAM, the bit positions which are set are used for matching and the bit positions that are clear are "don't cares". A space match occurs if, in the significant bit positions, the cycle address space number matches the ASN. Address space matching is schematically similar to logical address matching as shown in Figure 3-2.

#### 3.1.6 Segment Status Register (SSR)

Each descriptor has an 8-bit SSR. The SSR can be written to in two ways: using the load descriptor operation or indirectly using the descriptor pointer in a write status register operation. Each bit is labeled as control or status alterable. Bits 5 and 6 are reserved for future use.

|   | 7 | 6 | 5 | 4 | 3  | 2 | 1  | 0 | Addressed indirectly through |

|---|---|---|---|---|----|---|----|---|------------------------------|

| 1 | U |   |   | 1 | ΙP | М | WP | Е | the descriptor pointer       |

U (used) is set by the MMU if the segment was accessed since it was defined. This bit is status alterable.

Set: a) By a segment access (successful translation using the segment)

b) By an MPU write of "1"

Cleared: a) Reset (in segment #0 of master)

b) MPU write of "0"

If the I (interrupt) control bit is set, an interrupt is generated upon accessing the segment.

Set: a) MPU writes a "1"

Cleared: a) MPU writes a "0"

b) Reset (segment #0 of master)

IP (interrupt pending) is set if the I bit is set when the segment is accessed. IRQout is asserted if an IP bit, in one or more SSRs, is set and IE in the global status register (GSR) is set. IRQout is negated when all the IP bits in all SSRs are clear or IE is cleared. IP is status alterable and should be cleared by the interrupt service routine.

Set: a) Segment access and I is set

b) MPU writes a "1"

Cleared: a) MPU writes a "0"

b) Reset (in seament #0 of master)

c) E bit is a "0"

M The M (modified) bit is set by the MMU if the segment has been written to since it was defined. The M bit is status alterable.

Set: a) Successful write to the segment

b) MPU writes a "1"

Cleared: a) MPU writes a "0"

b) Reset (segment #0 in master)

WP If the WP (write protect) control bit is set, the segment is write protected. A write access to the segment with WP set will cause a write violation.

Set: a) MPU writes a "1"

Cleared: a) MPU writes a "0"

b) Reset (segment #0 in master)

E (enable) is a control bit which, when set, enables the segment to participate in the matching process. E can be cleared (the segment disabled) by a write to the SSR, but a load descriptor operation must be performed to set it.

Set: a) Load descriptor operation with AC7, bit #0 set

b) Reset (segment #0 in master)

Cleared: a) MPU writes a "0"

b) Unsuccessful load descriptor operation on this descriptor

c) Load descriptor operation with AC7, bit #0 cleared

#### 3.2 SYSTEM REGISTERS

The system registers consist of the address space table, accumulator, and miscellaneous registers which include global status register, local status register, descriptor pointer, result descriptor pointer, interrupt descriptor pointer, and interrupt vector register. Each of these registers is described below.

#### 3.2.1 Address Space Table (AST)

Each MMU has a local copy of the AST. This table is organized as 16 8-bit, read/write registers located at even byte addresses starting at address \$00. Each entry is programmed by the operating system with a unique address space number, each of which is associated with a task. During a memory access, the MMU receives a 4-bit function code (FC0-FC3) which is used to index into the AST to select the cycle address space number. This number is then used to check for a match with the ASN in each of the 32 descriptors within the MMU.

The MC68000 MPU and the MC68450 DMAC only provide a 3-bit function code, FC0-FC2. In a system with more than one bus master, the BGACK signal from the MPU could be inverted and used as FC3. This would result in the AST organization shown in Figure 3-4.

Figure 3-4. Address Space Table Organization

#### 3.2.2 Accumulator (AC0-AC8)

The accumulator (shown in Figure 3-1) is used to access the descriptors, perform direct translation, and latch information during a fault. The accumulator consists of nine 8-bit registers located at byte addresses from \$20 to \$28. The register assignments for each operation in which it participates is shown in Table 3-1.

| Register<br>Assignment | Load/Read Descriptor          | Direct Translation                  | Normal Translation (Fault)        | Address |  |

|------------------------|-------------------------------|-------------------------------------|-----------------------------------|---------|--|

| AC0                    | Logical Base Address (MSB)    | Logical Translation Register (MSB)  | Logical Address (MSB)             | \$20    |  |

| AC1                    | Logical Base Address (LSB)    | Logical Translation Register (LSB)  | Logical Address (LSB)             | \$21    |  |

| AC2                    | Logical Address Mask (MSB)    |                                     |                                   | \$22    |  |

| AC3                    | Logical Address Mask (LSB)    |                                     |                                   | \$23    |  |

| AC4                    | Physical Base Address (MSB)   | Physical Translation Register (MSB) |                                   | \$24    |  |

| AC5                    | Physical Base Address (LSB)   | Physical Translation Register (LSB) |                                   | \$25    |  |

| AC6                    | Address Space Number (ASN)    | Address Space Number (ASN)          | Cycle Address Space Number (CASN) | \$26    |  |

| AC7                    | Segment Status Register (SSR) |                                     |                                   | \$27    |  |

| AC8                    | Address Space Mask (ASM)      |                                     |                                   | \$28    |  |

Table 3-1. Accumulator Assignments for Operations

#### 3.2.3 Global Status Register (GSR)

The GSR is an 8-bit register used to reflect faults and to enable interrupts from an MMU. All MMUs maintain identical information in their GSRs. Bits 1, 2, 3, 4, and 5 are reserved for future use. The organization of the GSR is shown below. The GSR is located at address \$2D.

|     | 7 | 6  | 5 | 4 | 3 | 2 | 1_ | 0  | Address |

|-----|---|----|---|---|---|---|----|----|---------|

| GSR | F | DF |   |   |   |   |    | 1E | \$2D    |

- F (fault) is a status alterable bit that is set by the MMU whenever FAULTin is detected.

- Clearing the F bit automatically clears bits L4-L7 in the local status register.

- Set: a) Write violation detected in this MMU

- b) FAULTin detected

- c) ALLin detected (undefined segment access)

- d) MPU writes a "1"

- Cleared: a) Reset asserted

- b) MPU writes a "0"

- DF (double fault) is set if a FAULTin signal was detected with F set. DF is a status alterable bit.

- Set: a) Fault occurs and F was previously set

- b) MPU writes a "1"

- Cleared: a) Reset

- b) MPU writes a "0"

- If IE (interrupt enable) is set, the interrupt-request line is enabled. This is a read/write control bit.

- Set: a) MPU writes a "1"

- Cleared: a) Reset

- b) MPU writes a "0"

#### 3.2.4 Local Status Register (LSR)

The LSR is an 8-bit register which reflects information local to its MMU. The LSR can be globally written but the GAL, GAT, and LIP bits will not be affected. L4-L7 are cleared if F in the GSR is cleared on reset. The organization of the LSR is shown below. The LSR is located at address \$2F.

- RW RW is a status alterable bit which reflects the state of the R/W pin at the time FAULTin is asserted.

- Set: a) MPU writes a "1"

- b) When fault occurs during read of segment

- Cleared: a) Reset

- b) MPU writes a "0"

- c) When fault occurs during write of segment

- GAT (global accumulator for translate) is set by the MMU if ACO, AC1, and AC6 are globally consistent. See **4.5.3 Global Operations**.

- Set: a) If AC0, AC1, and AC6 are globally consistent (they were last modified as a result of a global write)

Cleared: a) Reset

b) If ACO, AC1, and AC6 are not globally consistent

GAL (global accumulator for load) is set if AC0, AC1, AC2, AC3, AC6, and AC8 are globally consistent.

Set: a) If ACO, AC1, AC2, AC3, AC6, and AC8 are globally consistent

Cleared: a) Reset

b) If ACO, AC1, AC2, AC3, AC6, and AC8 are not globally consistent

LIP (local interrupt pending) is set if one or more descriptors have IP set in their segment status registers.

Set: a) If IP is set in any descriptor

Cleared: a) Reset

b) If all IP bits are clear

L4-L7 The status information encoded in L4-L7 reflects the status of the MMU after the last event (an operation or fault). These bits are encoded and changed as a unit. They are cleared whenever the F bit in the GSR is cleared and are alterable by the MPU.

| L7 | L6 | L5 | L4 |     |                                                                                                                                                                                                                                                              |

|----|----|----|----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0  | 0  | 0  | 0  | NO  | The MMU was not the source of the last event.                                                                                                                                                                                                                |

| 1  | 0  | 0  | 0  | DT  | $\ensuremath{A}$ direct translation was locally successful. A match was found in one of the MMU descriptors.                                                                                                                                                 |

| 1  | 0  | 0  | 1  | LD  | A load descriptor fault occurred. A previously defined descriptor conflicts with the descriptor being loaded.                                                                                                                                                |

| 1  | 0  | 1  | 0  | USA | An undefined segment access was attempted. The logical address was not matched in any descriptor in the MMM.                                                                                                                                                 |

| 1  | 1  | 0  | 0  | WV  | A write violation occurred. A segment defined in the MMU was write protected and a write to that memory segment was attempted. The NVR bit in the RDP will show whether the USA or WV occurred in the MMU. See <b>3.2.6 Result Descriptor Pointer (RDP).</b> |

Set: a) Various bits set if DT, LD, USA, or WV occur

b) MPU writes a "1"

Cleared: a) Reset

b) MPU writes a "0"

c) When F bit in GSR is cleared

d) If MMU was not the source of the last event (NO)

#### 3.2.5 Descriptor Pointer (DP)

The DP is an 8-bit read/write pointer register located at address \$29. The five low-order bits identify the descriptor to be used in the load descriptor, read segment status (transfer descriptor), and write segment status operations. Bits 5, 6, and 7 are reserved.

The DP is initialized to \$00 on reset. It can be globally written by the MPU. The DP is loaded by the MMU with the number of the descriptor matched in a direct translation operation to allow a subsequent transfer descriptor operation to load the match descriptor into the accumulator. See **4.6.3 Global Operation** and **4.6.3.3 Direct Translation**.

#### 3.2.6 Result Descriptor Pointer (RDP)

The RDP is an 8-bit, read-only register that identifies a descriptor involved in the following events: a write violation, a load descriptor failure, or a direct translation success. The RDP is loaded from a priority encoder which determines the highest priority descriptor involved. For example, in a load descriptor operation, more than one descriptor currently in the MMU may collide with the descriptor being loaded. Only the number of the highest priority descriptor will be loaded into the RDP. Descriptor 0 is considered to be the highest priority and 31 is the lowest.

The RDP bit assignments are shown below. Bits 5 and 6 are reserved. The RDP is initialized to \$80 on reset. The RDP is located at address \$3B.

NVR If no descriptor is selected by the priority encoder when the RDP is loaded, NVR (no valid result) is set; otherwise, it is cleared. This bit is status unalterable.

Set: a) Rese

b) No result from WV, LD, or DT

Cleared: a) AWV, LD failure of DT success in MMU

R0-R4 R0-R4 encode the number of the descriptor selected by the priority encoder.

#### 3.2.7 Interrupt Descriptor Pointer (IDP)

The IDP is an 8-bit read-only register that is read to determine which descriptor caused an interrupt. Each time it is read, the IDP is loaded from the priority encoder with the highest-priority descriptor which has IP set in its SSR. If no descriptor has IP set, the no valid interrupt (NVI) bit is set. See 4.6.2.1 Interrupt Acknowledge.

The bit IDP assignments are shown below. Bits 5 and 6 are reserved. The IDP is located at address \$39.

NVI NVI is set if no descriptor has IP set; otherwise, it is cleared.

10-14 These bits encode the number of the descriptor selected by the priority encoder.

#### 3.2.8 Interrupt Vector Register (IVR)

The IVR is an 8-bit read/write register containing the interrupt vector. Its contents are placed on the data lines, D0-D7, during the interrupt acknowledge operation to provide the processor with a vector number. The IVR is initialized to \$0F (the MC68000 uninitialized-device vector number) on reset. The IVR is located at address \$2B.

|     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |                 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----------------|

| IVR | IV7 | IV6 | IV5 | IV4 | IV3 | IV2 | IV1 | IV0 | Address<br>\$2B |

### SECTION 4 MMU FUNCTIONAL DESCRIPTION

#### 4.1 SINGLE-MMU SYSTEMS

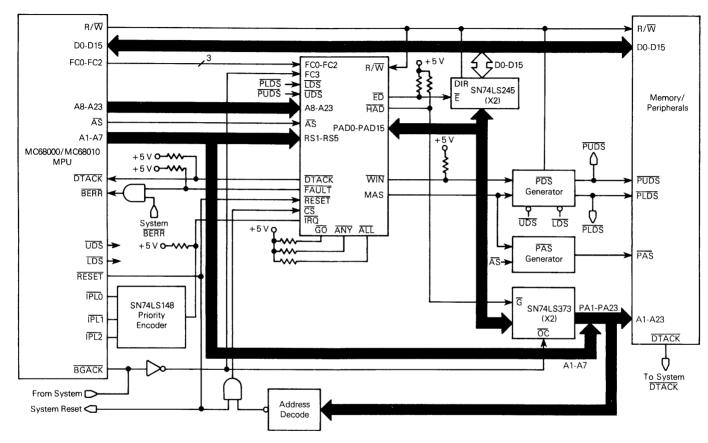

The memory management mechanism can be comprised of one or more memory management units. Implementing memory management using the MC68000 or MC68010 MPUs and a single MC68451 is straightforward. Two SN74LS245 type bidirectional buffers are needed to demultiplex the physical address/data port (PAD0-PAD15). These are directly controlled by the enable data  $(\overline{\text{ED}})$  and read/write  $(R/\overline{\text{W}})$  lines. Two SN74LS373 type transparent latches are used to latch the translated address when the PAD port is needed to transfer data to or from the MPU. These latches are controlled by the hold address  $(\overline{\text{HAD}})$  line. A circuit diagram of a single-MMU system is shown in Figure 4-1.

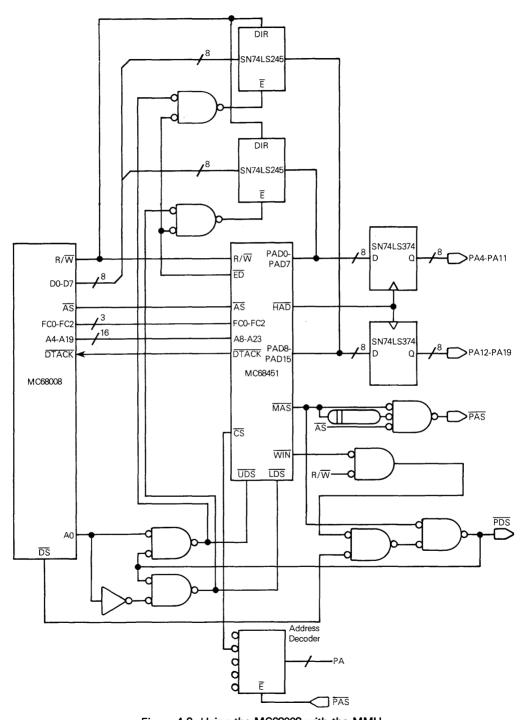

The MMU may also be used with the MC68008 8-bit data bus version of the MC68000. This requires only a few gates to synthesize the upper and lower data strobe signals  $(\overline{\text{UDS}})$  and  $\overline{\text{LDS}}$  from address line A0 and data strobe  $(\overline{\text{DS}})$  on the MC68008. Since there is only one data strobe in an MC68008 system, the physical data strobe generation is somewhat simpler; otherwise, the circuit is identical to that of the MC68000 system. A circuit diagram of a single-MMU system using the MC68008 MPU is shown in Figure 4-2.

#### 4.2 MULTIPLE-MMU SYSTEMS

If more than 32 descriptors are needed for performance enhancement reasons, multiple MMUs may be configured in a system. The number of MMUs that can be used is not logically constrained. In practice, buffer drive limitations limit the number to six MMUs without using additional external buffering.

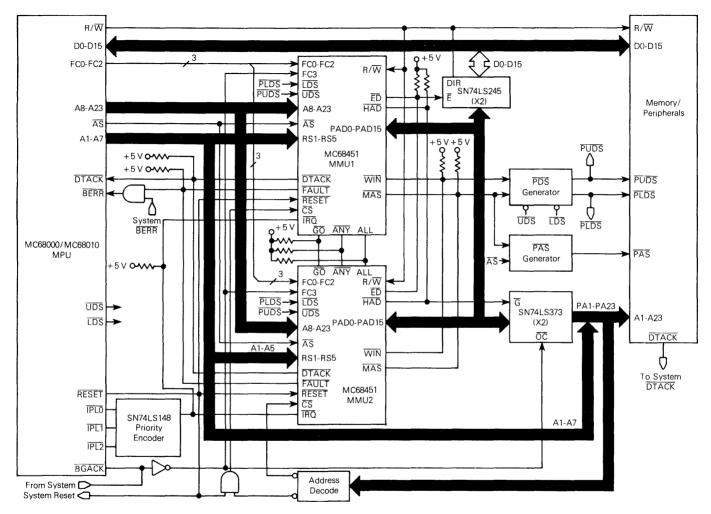

A circuit diagram showing two MC68451s in a system with the MC68000 or MC68010 is shown in Figure 4-3. Notice that the data buffers and address latches are shared by both MMUs and need not be duplicated. The  $\overline{\text{GO}}$ ,  $\overline{\text{ANY}}$ , and ALL lines are bused together to provide the inter-MMU handshake necessary for the global operations as outlined below. Notice that only one of the MMUs is chip-selected on  $\overline{\text{RESET}}$ . This selects the master out of reset. For more information refer to **4.5.1** The Reset State.

In order to perform its operations, some of the information in MMU registers must be global. That is, it must be duplicated in all the MMUs in the system. For example, the address space table must be global to insure that the address space numbers are common to all MMUs. To allow this, certain operations are defined as global. Any system register that can be written, is written globally. This includes the accumulator, the address space table, the descriptor pointer, the interrupt vector register, the global status register, and the local status register. The result descriptor pointer and the interrupt descriptor pointer are read only and, therefore, are local and not global.

Figure 4-1. Single-MMU System with MC68000 or MC68010

Figure 4-2. Using the MC68008 with the MMU

Figure 4-3. Sample Circuit Diagram of a Two-MMU System with the MC68000 or MC68010

The  $\overline{\text{ANY}}$ , ALL, and  $\overline{\text{GO}}$  signal lines are used to connect multiple MMUs to form the MMM. The MMM uses these input/output signals to communicate information between MMUs and maintain functional unity. The  $\overline{\text{GO}}$  (global operation) pin is used to establish the master-slave relationship between MMUs for a given operation. The  $\overline{\text{ANY}}$  signal is detected as true if any MMU asserts it, allowing MMUs to report conditions that are important in even one device. The ALL signal is detected as true only if all MMUs assert it. It is used to verify that all MMUs in the system have performed some operation or are in the same state. A sample circuit diagram of a two-MMU system using the MC68000 or MC68010 is shown in Figure 4-3.

During each global operation, one MMU is specified as the master; all others are designated as slaves. The MMU which has its chip select  $(\overline{CS})$  asserted becomes the master by asserting the  $\overline{GO}$ out signal. This signals the other MMUs that they are slaves for that operation. Note that all MMUs may be accessed and, therefore, any one may be the master for a given operation.

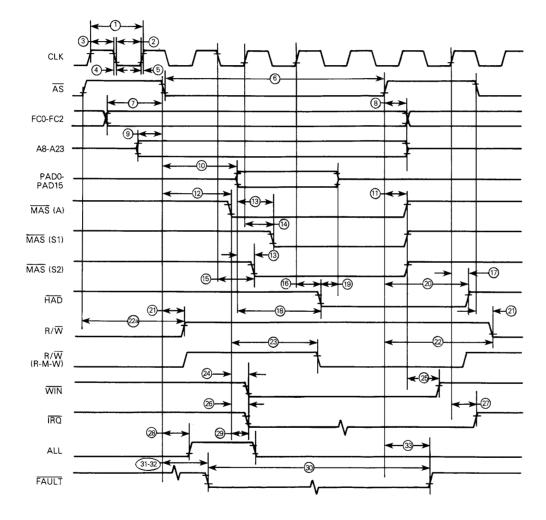

#### 4.3 MMU TIMING

The MC68451 is a hybrid machine. The normal translation function is implemented in combinational logic for maximum speed. The operations (reading and writing registers, etc.) are implemented with a synchronous finite state machine. Due to the asynchronous nature of the signals used to communicate between MMUs, the timing of these operations will vary due to a number of factors, including the placement of  $\overline{AS}$ , the speed of translations, the relationship of  $\overline{CS}$  to the internal clocks, and the need to internally synchronize the input signals. Because of this, timing diagrams are shown with breaks to indicate a variable number of clock periods between events.

#### 4.4 MMU FLOW DIAGRAM

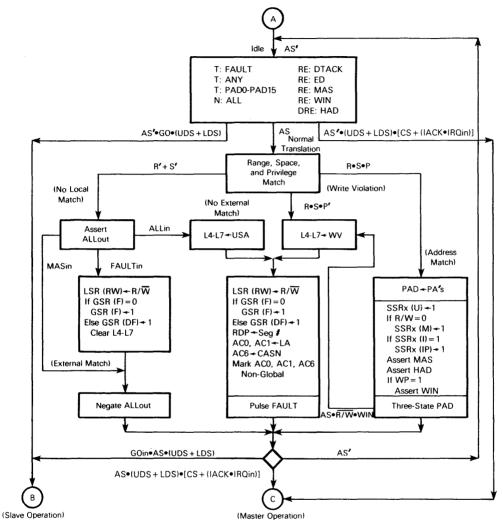

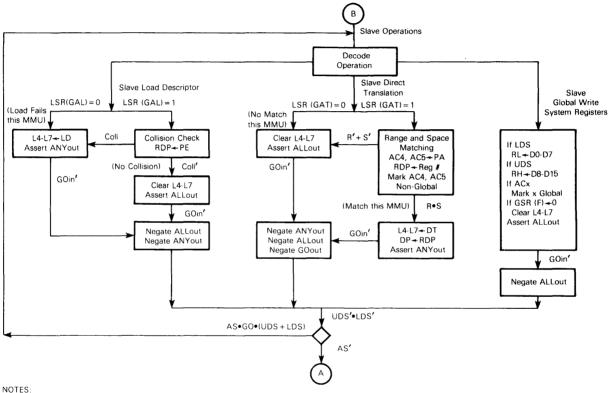

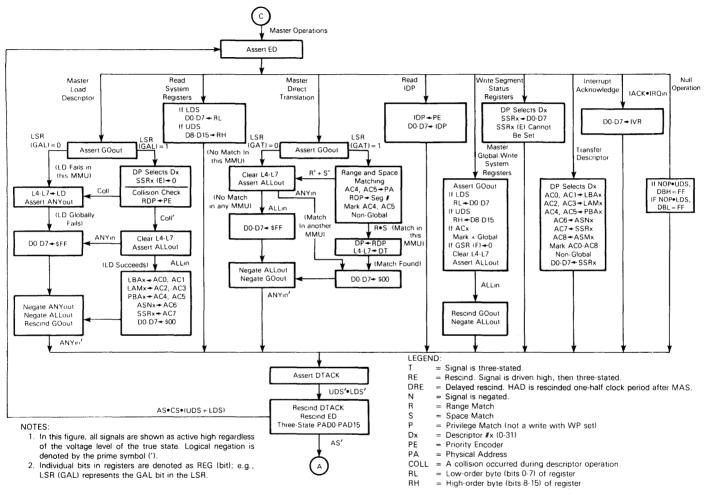

In order to give a functional description of the MMU, the flow diagrams of the device are given in Figure 4-4. Each box contains certain actions (loading registers, asserting signals, etc.) and the paths leading from it are labeled with a signal name or logical expression of signal names. If the signal or expression is true, that branch is taken. The only timing information given is the chronological order in which events occur. The length of each operation, given in system clock cycles, is shown in Table 4-1.

#### NOTE

In Figure 4-4, all signals are shown as active high regardless of the voltage level of the true state. Logical negation is denoted by the prime symbol (').

#### 4.5 MMU FUNCTIONAL STATE

At any time an MMU may be in one of five states: reset, idle, normal translation, local operations, or global operations. In a global operation, an MMU may be a master (if the  $\overline{CS}$  signal is asserted) or a slave (if  $\overline{GO}$ in is asserted). In addition, two actions can occur regardless of the current state:

- 1. If RESET is asserted, the reset operation begins. The MMM will remain in the reset state until RESET is negated.

- 2. IRQout is asserted if the local interrupt pending bit in the local status register and interrupt enable in the global status register are set; otherwise, it is placed in the high-impedance state and should be negated with a pullup resistor.

#### NOTES:

- 1. In this figure, all signals are shown as active high regardless of the voltage level of the true state. Logical negation is denoted by the prime symbol (').

- 2. Individual bits in registers are denoted as REG (bit); e.g., LSR (GAL) represents the GAL bit in the LSR.

#### LEGEND:

| LEGEND. |    |                                  |    |   |                                   |      |   |                             |  |

|---------|----|----------------------------------|----|---|-----------------------------------|------|---|-----------------------------|--|

| T       | == | Signal is three-stated.          | Ν  | = | Signal is negated.                | PE   | = | Priority Encoder            |  |

| RE      | =  | Rescind. Signal is driven high,  | R  | = | Range Match                       | PA   | = | Physical Address            |  |

|         |    | then three-stated.               | S  | = | Space Match                       | COLL | = | A collision occurred during |  |

| DRE     | =  | Delayed rescind. HAD is rescind- | Ρ  | = | Privilege Match (not a write with |      |   | descriptor operation.       |  |

|         |    | ed one-half clock period after   |    |   | WP set)                           | RL   | = | Low-order byte of register  |  |

|         |    | MAS.                             | Dx | = | Descriptor #x (0-31)              | RH   | = | High-order byte of register |  |

Figure 4-4. MMU Flow Diagram (Sheet 1 of 3)

- 1. In this figure, all signals are shown as active high regardless of the voltage level of the true state. Logical negation is denoted by the prime symbol (\*).

- 2. Individual bits in registers are denoted as REG (bit); e.g., LSR (GAL) represents the GAL bit in the LSR.

### LEGEND:

| T<br>RE | <ul> <li>Signal is three-stated.</li> <li>Rescind. Signal is driven high,<br/>then three-stated.</li> </ul> | DRE    | <ul> <li>Delayed rescind. HAD is<br/>rescinded one-half clock<br/>period after MAS.</li> </ul> | S<br>P | <ul><li>Space Match</li><li>Privilege Match (not a write with WP set)</li></ul> |          | Physical Address A collision occurred during descriptor operation. |

|---------|-------------------------------------------------------------------------------------------------------------|--------|------------------------------------------------------------------------------------------------|--------|---------------------------------------------------------------------------------|----------|--------------------------------------------------------------------|

|         |                                                                                                             | N<br>R | <ul><li>Signal is negated.</li><li>Range Match</li></ul>                                       |        | = Descriptor #x (0-31)<br>= Priority Encoder                                    | RL<br>RH | Low-order byte of register High-order byte of register             |

Figure 4-4. MMU Flow Diagram (Sheet 2 of 3)

Figure 4-4. MMU Flow Diagram (Sheet 3 of 3)

Table 4-1. Length of Operations

| Operation                                                   |     | ngth<br>Periods) |

|-------------------------------------------------------------|-----|------------------|

| Single MMU                                                  |     |                  |

|                                                             | Min | Max              |

| Read System Register (Except IDP)                           | 13  | 15               |

| Read Interrupt Descriptor Pointer                           | 21  | 23               |

| Write System Register (Except Segment Status)               | 17  | 19               |

| Write to Segment Status Register                            | 11  | 13               |

| Load Descriptor (No Error)                                  | 33  | 35               |

| (Collision Error)                                           | 27  | 29               |

| (No GAL)                                                    | 21  | 23               |

| Direct Translation (No Error)                               | 25  | 27               |

| (Undefined Segment)                                         | 27  | 29               |

| (No GAT)                                                    | 19  | 21               |

| Read SSR and Transfer Descriptor                            | 17  | 19               |

| Interrupt Acknowledge                                       | 13  | 15               |

| Null Operation (Read)                                       | 11  | 13               |

| Null Operation (Write)                                      | 9   | 11               |

| Multiple MMU                                                |     | ·                |

|                                                             | Min | Max              |

| Read System Register (Except IDP)                           | 13  | 15               |

| Read Interrupt Descriptor Pointer                           | 21  | 23               |

| Global Write System Register (Except Segment Status)        | 21  | 29               |

| Write Segment Status                                        | 11  | 13               |

| Load Descriptor (No Error)                                  | 35  | 43               |

| (Match-{m}, No Err-{s})                                     | 27  | 29               |

| (Match - {m}, GAL - {s})                                    | 35  | 43               |

| (Match = {s}, No Err = {m})                                 | 39  | 51               |

| (No GAL – {m}, Match – {s})                                 | 21  | 23               |

| (No GAL – {m}, Match (5)<br>(No GAL – {m}, No Err – {s})    | 21  | 23               |

| (No GAL – {s}, No Err – {m})                                | 31  | 43               |

| (No GAL – {s}, No GAL – {m})                                | 27  | 31               |

| Direct Translation (Match—{m}, No Err—{s})                  | 25  | 27               |

| (Match - {s}, No Err - {m})                                 | 39  | 51               |

| (Match = {s}, No En = {in})<br>(Match = {m}, No GAT = {s})  | 25  | 27               |

| (Match = {iii}, No GAT = {s})                               | 39  | 51               |

| (No Match = {si, No GA1 = {iii}                             | 31  | 39               |

| (No Match={fil, s}) (No Match={s}, No GAT={m})              | 31  | 39               |

| (No Match={s}, No GAT={iii}/<br>(No Match={m}, No GAT={si}) | 27  | 33               |

|                                                             | 27  | 33               |

| (No GAT—{m}, No GAT—{s})                                    | 17  | 19               |

| Read SSR and Transfer Descriptor                            |     |                  |

| Interrupt Acknowledge                                       | 13  | 15               |

| Null Operation (Write)                                      | 9   | 11               |

| Null Operation (Read)                                       | 11  | 13               |

- Length of operations are given in system clock periods. The length of the operations is defined from the assertion of CS to the

assertion of DTACK except in the case of interrupt acknowledge operations. In this case, the timing is given from TACK to DTACK.

- 2. These operation lengths assume that all MMUs have a common system clock. The actual length of a given operation will depend upon when CS (or IACK) is asserted at the MMU. In the case of multiple-MMU systems, the length will also depend on the rise and fall times of the inter-MMU handshake signals and their relationship to the internal clocks of the MMU.

- 3. In multiple MMU operations, the master is denoted by {m} and the slave is denoted by {s}. The notes 'no GAL' and 'no GAT' indicate that bit is cleared.

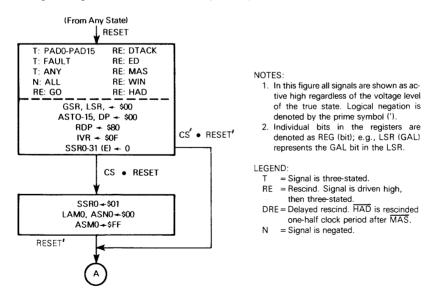

### 4.5.1 The Reset State

Asserting RESET will initiate the reset sequence regardless of the state of the MMU. During reset, GO, DTACK, ED, MAS, HAD, and WIN are rescinded. The PAD port, FAULT, and ANY are placed in the high-impedance state. Pullup resistors on FAULT and ANY keep these signals negated. The ALL pin is driven low to negate it.

The GSR, LSR, DP, and the entire address space table are initialized to \$00. The RDP is initialized to \$80 and the IVR to \$0F. All descriptors are disabled by clearing the enable bits in their segment status registers.

In order to allow the address bus to function before the operating system can initialize the MMM, one MMU is selected to have descriptor #0 initialized so that it maps any logical address unchanged to the physical address bus. The MMU is selected for this by having its chip-select line asserted during reset. This circuit is shown in Figure 4-3.

Descriptor 0 in the selected MMU will have had its LAM and ASN cleared to \$00, its ASM set to \$FF, and the enable bit set. Because of this, the logical address passes to the physical address bus (via descriptor #0) without alteration. The enable bits of descriptors 1-31 are cleared to disable them and their contents remain uninitialized. If the chip selected  $(\overline{CS})$  is not selected during reset, the enable bits in all descriptors are cleared and no descriptor is initialized.

A flow diagram for the reset state is given in Figure 4-5.

#### NOTE

In Figure 4-5, all signals are shown as active high regardless of the voltage level of the true state. Logical negation is denoted by the prime symbol (').

Figure 4-5. Reset Flow Diagram

### 4.5.2 The Idle State

The idle state is used to terminate bus accesses and prepare for new ones. The MMU is "backed-off" the bus; i.e., the data transceivers are placed in the high-impedance state and the address latches are put into the transparent mode. The outputs are driven to the same levels as in reset except that  $\overline{\text{HAD}}$  is rescinded one-half clock after  $\overline{\text{MAS}}$  to provide address hold time.

While in the idle state, the MMU uses the function code inputs to index into the AST to provide the cycle address space number. If  $\overline{AS}$  is asserted, a normal translation is performed. If  $\overline{AS}$  is negated and  $\overline{CS}$ ,  $\overline{IACK}$ ,  $\overline{IRQ}$ in,  $\overline{GO}$ , and the data strobes indicate an access from the physical bus, an operation is performed. For further information, see **4.6 MMU OPERATIONS**.

### 4.5.3 Normal Address Translation

At the start of a bus cycle, the processor presents the logical address,  $R/\overline{W}$ , and the function code to the MMM. The function code is used to index into the address space table to select the cycle address space number. When  $\overline{AS}$  is asserted, the normal translation phase begins by sending the cycle address space number, the logical address, and  $R/\overline{W}$  to each descriptor for matching.

#### NOTE

The function codes must be valid before  $\overline{AS}$  is asserted to allow for the table lookup. Current versions of the MC68000 provide this setup time; however, early mask sets (R9M, T6E, BF4) do not. With these early mask sets,  $\overline{AS}$  must be delayed to the MMU.

- **4.5.3.1 MATCHING.** Matches can occur in two areas: range and space. A range match occurs if, in each bit position in the LAM which is set, the incoming logical address matches the LBA. A space match occurs if, in each bit position in the ASM which is set, the cycle address space number matches the ASN

- **4.5.3.2 SUCCESSFUL TRANSLATION.** An address match occurs if there is a range match and a space match. A write violation occurs if a write is attempted to a write-protected segment. If there is an address match in a descriptor and no write violation, the physical address is formed from the PBA of that descriptor and the logical address. The logical address is passed through in those bit positions in the LAM which are clear (the "don't cares"). In the other bit positions, the PBA is gated out to the physical address bus.

The U and, if the cycle was a write, the M bits in the segment status register are set. If the I bit is set, then the IP bit is set.  $\overline{\text{WIN}}$  is asserted if the WP bit is set and the cycle was a read or a read-modify-write. If the cycle was a write,  $\overline{\text{MAS}}$  is not asserted to prevent the write from modifying data.

After the physical address is stable,  $\overline{MAS}$  is asserted to indicate a valid address is on the bus.  $\overline{HAD}$  is asserted to hold the address stable on the latches and the PAD0-PAD15 lines are then placed in the high-impedance state. If  $\overline{AS}$  is then negated, the cycle has terminated and the MMU returns to the idle state. A functional timing diagram for a normal translation in a two-MMU system is shown in Figure 4-6. If  $\overline{AS}$  is not negated, the cycle can continue in three ways:

- 1. If  $\overline{\text{CS}}$  or  $\overline{\text{IACK}}$  and  $\overline{\text{IRQ}}$ in are asserted, the MMU will begin an operation as a master. See **4.6.3 Global Operations.**

- 2. If GOin is detected by an MMU, it will begin a slave operation. See 4.6.3 Global Operations.

- 3. If a high-to-low transition is detected on R/\overline{W} (indicating a write) \overline{AS} remains asserted, and the matched segment is write protected, a write violation occurs. The \overline{WIN} signal is asserted to protect the memory. This would be the result of a read-modify-write bus cycle on a protected segment.

- **4.5.3.3 WRITE VIOLATION.** If an address match occurs but the bus cycle was a write to write-protected segment, a write violation occurs. In this case, the RDP is loaded from the priority encoder, F is set in the GSR, and DF is set if F was previously set. The state of the  $R/\overline{W}$  line is latched into the RW bit of the LSR and L4-L7 are encoded to indicate write violation (WV). The  $\overline{FAULT}$  out signal is then asserted for five clock cycles or until  $\overline{AS}$  is negated, whichever is longer.

The logical address is latched into AC0 (MSB) and AC1 (LSB) of the accumulator (see Table 3-1). The cycle address space number is latched into AC6. These registers are marked as non-global with respect to the GAT and GAL bits. If the  $\overline{\text{FAULT}}$  pin has been connected to the  $\overline{\text{BERR}}$  pin on the MC68000,  $\overline{\text{AS}}$  will be negated as the MPU begins the bus error exception processing. When  $\overline{\text{AS}}$  is negated, the MMU will enter the idle state.

A functional timing diagram for a translation with a write violation is shown in Figure 4-7. The breaks in the diagram reflect the uncertainty due to the deskewing of the input signals from other MMUs

- **4.5.3.4 NO ADDRESS MATCH.** If none of the descriptors in an MMU has an address match, that MMU asserts ALLout, and monitors  $\overline{\text{MAS}}$ in,  $\overline{\text{FAULT}}$ in, and ALLin. There are then three possibilities:

- The access was successfully translated in another MMU. See 4.5.3.5. EXTERNAL TRANSLATION.

- 2. The access caused a write violation in another MMU. See **4.5.3.6 EXTERNAL WRITE VIOLATION.**

- The access was to a globally undefined segment. See 4.5.3.7 UNDEFINED SEGMENT ACCESS.

- **4.5.3.5 EXTERNAL TRANSLATION.** If MAS in becomes asserted, the access was successfully translated by another MMU. The MMU negates ALLout and prepares to end the normal translation phase. The cycle can then continue in one of three ways:

- 1. If AS becomes negated, the MMU returns to the idle state.

- 2. If  $\overline{CS}$ , or  $\overline{IACK}$  and  $\overline{IRQ}$  in are asserted, the MMU begins an operation as a master.

- 3. If GOin is detected true, the MMU begins an operation as a slave.

Figure 4-6. Normal Translation Timing on a Two-MMU System

Figure 4-7. Write Violation Timing

**4.5.3.6 EXTERNAL WRITE VIOLATION.** If the FAULTin line is detected true (low), a write violation occurred in another MMU. The detecting MMU then sets the F bit in the GSR and the DF bit if the F bit was already set. R/W is latched into the RW bit of the LSR, and L4-L7 are cleared to show that the violation did not take place in the MMU. The cycle can then continue in one of the three ways described in **4.5.3.5 EXTERNAL TRANSLATION.**

**4.5.3.7 UNDEFINED SEGMENT ACCESS.** If ALLin is detected true (high), none of the other MMUs in the system obtained a match, indicating the segment is globally undefined. The MMU sets the F bit in the GSR and the DF bit if F was set previously.  $R/\overline{W}$  is latched into the RW bit of the LSR and L4-L7 are encoded to show a USA.

The logical address (A8-A23) is latched into the accumulator, AC0 (MSB) and AC1 (LSB), and the cycle address space number is latched into AC6. These registers are marked non-global with respect to the GAL and GAT bits.

All MMUs assert the FAULT line for five clock periods or until  $\overline{AS}$  is negated, whichever is longer. To assure the detection of ALLin by all MMUs, ALLout remains asserted for two clock cycles after ALLin is detected true. ALLout is negated before the beginning of the FAULT pulse. When  $\overline{AS}$  is negated, the MMM returns to the idle state.

A functional timing diagram for an undefined segment access is given in Figure 4-8. The breaks in the diagram reflect the uncertainty due to the deskewing of the input signals from other MMUs.

Figure 4-8. Undefined Segment Access Timing

### 4.6 MMU OPERATIONS

Table 4-2 shows the operations which can be performed. Each operation is initiated by the access of an address given on the register select lines RS1-RS5 and the upper and lower data strobes. The access can be from either the logical or physical address bus. In a multiprocessor system, an external processor could access the MMM from the physical address bus. If the access is from the logical address bus, and address translation is first performed. If the access is from the physical address bus, the operation state is entered directly from the idle state.

Table 4-2. Summary of MMU Functions

| Function               | Summary                                                                                                                   |

|------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Idle                   | The MMU backs off the bus to prepare for a new access.                                                                    |

| Reset                  | The MMU is pre-emptively initialized.                                                                                     |

| Normal Translation     | The MMU attempts to translate an access from the logical address bus.                                                     |

| Operations             | The MMU is accessed from the logical or physical bus.                                                                     |

| Write System Registers | An operation to globally write system registers.                                                                          |

| Read System Registers  | An operation to read the system registers.                                                                                |